#### SECTION VI

#### V24 SERIAL CONTROL UNIT

# 6.1 GENERAL

The V24 Serial Control Unit (V24-CU), located on the CPU card, interfaces an Operator's device with the CPU. The V24-CU converts between eight-bit parallel CPU characters (at +5/0V) for the CPU and bit-serial data (at +12/-12V) for the device. The V24-CU can provide parity bit insertion and checking; this feature is plug-programmable by means of U-links on the CPU/CU card.

Operating speed is also plug-programmable, with the possibilities:

110 baud, for ASRV24

600 baud, for PER 3100

1200 baud

2400 baud

4800 baud

9600 baud

The V24-CU uses direct interface connections with the CPU for address, command, and data to minify GP-Bus utilization. The address and commands are received directly from the CPU K-register. CU/CPU data is received directly from the least-significant half of the L-register (L8-15) and sent directly to the CPU via the C-selector.

# 6.2 Channel and Interrupts

The CU operates via the system programmed channel, under direct control of the CPU. The CU sends an interrupt (INTSERN) to the CPU to request each character transfer and to indicate when it is in Wait Status mode.

## 6.3 Serial Data Format

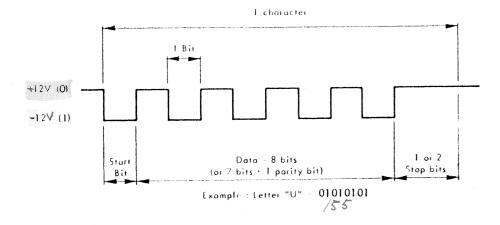

The bit-serial data format for a single character is shown in Figure 6-1. The eighth "Data" bit may be either an actual CPU data bit or it may be a parity bit supplied and checked by the V24-CU. The parity bit, if used, can be either even or odd. Either one or two stop bits may be selected (by a plug on the card) to conform to the device requirements.

Figure 6-1 Serial Data Format

A logic One is represented by a low level (-12V) and a logic Zero is represented by a high level (+12V). When no character is being exchanged, the line is High. Characters may be transferred end-to-end or may be separated by any amount of gap.

## 6.4 CPU INTERFACE AND CONTROL

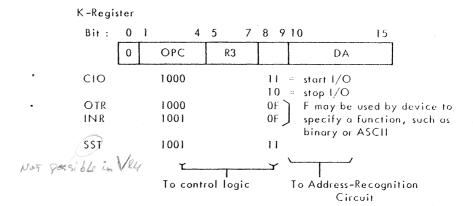

The V24-CU operations are controlled by CPU I/O instructions (CIO Start, CIO Halt, OTR, INR, SST). These instructions are format-0, type T8. The instruction word contains address and control information which is sent directly to the CU on the K lines 4, 8-15, as follows:

Additional control is provided directly from the CPU D-register. Bit D15 indicates input (D15 high) or output (D15 low) operations. This bit controls the setting of the CU flip-flop IN/OUT during a CIO Start operation. Bit D10 is set during a CIO Start operation to indicate Echo mode (routing the device input data directly back to the device during input data transfers).

6.5 The CU detects its address from K10-15 when it receives CPU timing signal TMPR from the CPU. The CU recognizes its address, generates internal Address-Recognized signal TYARE/N, and sends AREDELA back to the CPU. The address code is determined by the addressing U-links. If the command is accepted, the CU sends signal TYAC back to the CPU; if the command is not accepted, TYAC is not sent and no other action is performed by the CU.

## 6.6 OPERATION

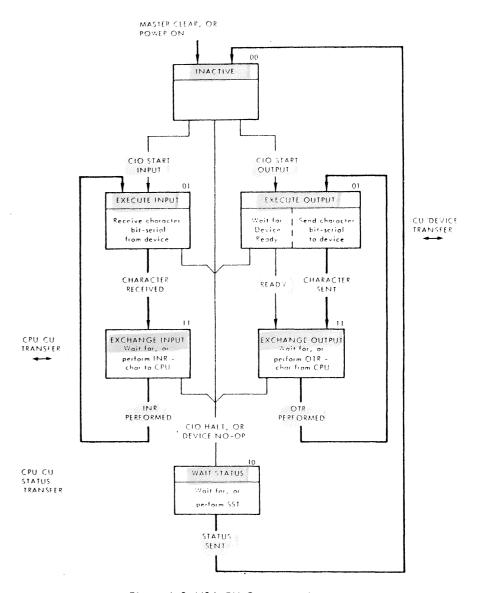

The V24-CU operates in six different states, as follows:

| Operational<br>State | FO, | /F1 | Function                                                                                      |

|----------------------|-----|-----|-----------------------------------------------------------------------------------------------|

| Inactive             | 0   | 0   | The CU is inactive.                                                                           |

| Execute-In           | 0   | 1   | The CU is waiting for or receiving a character bitserial from the device.                     |

| Exchange-In          | 1   | 1   | The CU is waiting for or performing an INR command (Character to CPU).                        |

| Execute-Out          | 0   | 1   | The CU is transmitting one character bit-serial to the device, or is waiting for a free line. |

| Exchange=Out         | 1   | 1   | The CU is waiting for or performing an OTR command (Character from CPU).                      |

| Wait Status          | ı   | 0   | The CU is waiting for or executing an SST command.                                            |

The operating flow is shown in Figure 6-2. The CU is set to the Inactive state by master clear (MCL/RSL), including at system power-on time. When the CU receives a CIO Start command (input or output), it goes to the Execute State if the device is operable; if the device is inoperable, the CU switches to Wait Status state.

- 6.7 In input mode, the CU goes to Execute-Input state and receives or waits for a character from the device. When the character has been received, the CU switches to Exchange-Input mode and transfers the character to the CPU, with an INR command.

- 6.8 In output mode, the CU switches from Execute to Exchange state as soon as the device is ready. The CU waits for, or receives, an OTR command with one character from the CPU. The CU switches to Execute-Output state to transfer the character bit-serial to the device, and switches back to Exchange state.

Figure 6-2 V24-CU Operational States

6.9 When the CU receives a CIO Halt command from the CPU, it goes to Wait Status state. The switch to Wait Status is not delayed if CIO Halt is received while the CU is exchanging a character with the device, because the exchange is performed independently by the UART chip once the CU has initiated the operation. If a new exchange is requested, however, it must wait for the end of the current transmission, when FTEOC is reset by the TEOC signal from the UART chip.

#### 6.10 LOGIC DESCRIPTION

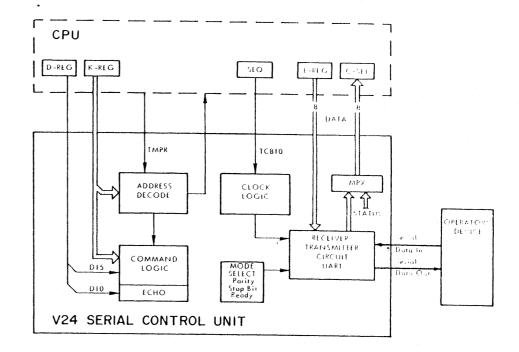

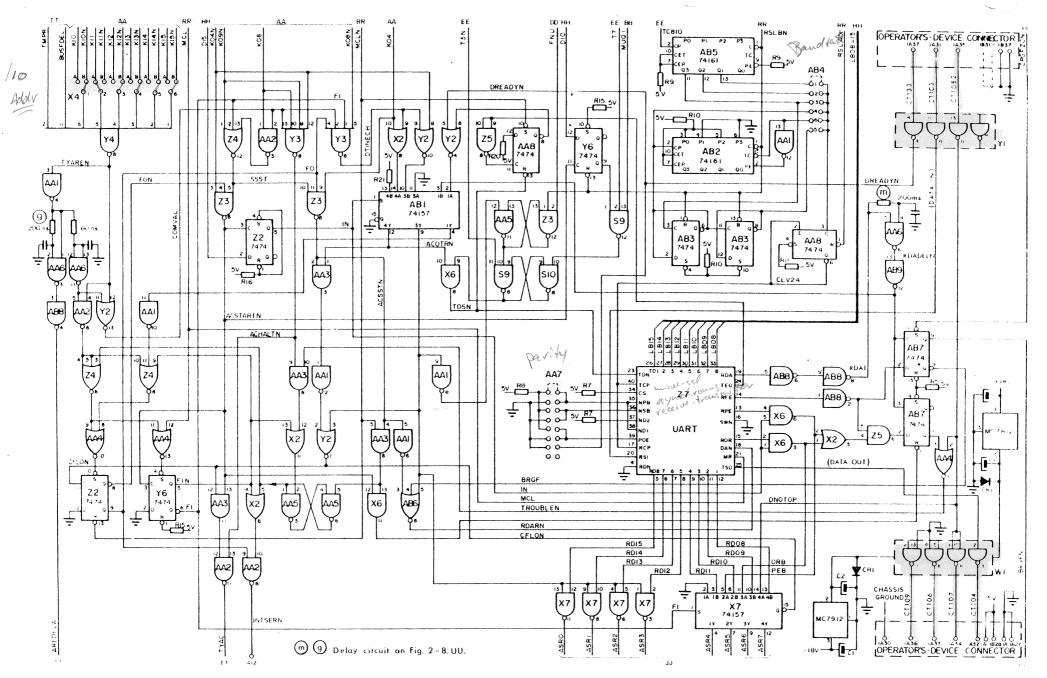

A block diagram of the V24-CU is shown in Figure 6-3. Detailed logic is provided in Figure 6-4.

#### 6.11 Data Path

Output data is 8-bit parallel from the CPU L-register direct to the integrated receiver/transmitter circuit UART in the CU. The UART circuit outputs the character bit-serial (with the appropriate start, stop, and parity bits added) to the device on the CT104 line. Input data is received bit-serial from the device via the CT103 line. The input character is assembled by the UART circuit (with start, stop, and parity bits removed) and sent 8-bit parallel to the CPU C-selector.

6.12 The input data path to the CPU is via a type 74157 multiplexer circuit. This circuit is used to place status bits on the data lines during an SST command. Voltage conversion, from +5/0V logic to the +12/-12V used by the device, is performed by the type 1488 output inverters and the 1489A input inverters.

#### 6,13 Character Conversion

Character conversion between bit-serial and bit-parallel is performed directly by receiver/transmitter circuit UART. During output operations, the UART circuit adds the start bit (logical zero) and stop bits (logical 1) to each character.

Either one or two stop bits are added, depending on the U-link selection for the NSB input of the UART. (Two stop bits are normal, but a device may require just

Figure 6-3 V24 Serial CU Block Diagram

- one.) During input operations, the UART circuit strips off the same start and stop bits that it is set to add during output operations.

- 6.14 Transmitting speed is controlled by CU clock logic which is synchronized with the CPU clock. The basic clock signal is TC810 from the CPU. This clock rate is divided by type 74161 counters and flip-flops to provide clock rates for 110, 600, 1200, 2400, 4800, and 9600 baud. The desired rate is selected by positioning a U-link jumper. The selected clock signal drives the UART circuit, via flip-flop CLV24, through the TCP and RCP inputs.

# 6.15 Parity

The UART circuit can be manually programmed (by means of circuit U-links) to operate without parity, or to insert and check either even or odd parity. With no-parity selected (high level to the UART inputs NPB and ND1), all eight data bits to and from the CPU are sent and received as data bits on the device data lines. If the U-link is set to select parity operation (NPB/ND1 low), a second U-link at the POE input determines whether even or odd parity is to be used.

6.16 Whenever parity is selected, the UART circuit ignores the least-significant bit to and from the CPU (bit 15). For output operations, the UART circuit determines the parity of the seven data bits used and places the resulting parity bit in place of the eighth data bit with the serial character to the device. For input operations, the UART circuit checks the parity of the first seven data bits received, and compares the result with the eighth (parity) bit. The UART circuit indicates an error by activating the PE signal. A parity error sets the CHIPER and FHALT flip-flops and switches the CU to Wait Status state.

### 6.17 Device Interface

All CU-Device signals are via connector 1, as follows:

| Conn.                | Line                    | Signal                                                                                                                                                                                    |  |  |

|----------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1A30                 | CT101                   | Mechanical Ground, to/from GP Bus connector 3                                                                                                                                             |  |  |

| 1831<br>to<br>1837   | CT102                   | Ground                                                                                                                                                                                    |  |  |

| 1A27<br>1B27         |                         | Signal Ground                                                                                                                                                                             |  |  |

| 1A28<br>1B28         |                         | +5V                                                                                                                                                                                       |  |  |

| 1A31                 | CT103                   | Data In, serial data from device to CU.                                                                                                                                                   |  |  |

| 1A32                 | CT104                   | Data Out, serial data from CU to device.                                                                                                                                                  |  |  |

| 1A33<br>1A34<br>1A36 | CT106<br>CT107<br>CT109 | High = CPU switched on.<br>High when CT1082 is high.<br>High = CPU switched on.                                                                                                           |  |  |

| 1A35                 | CT1082                  | Operable, high when device is connected and switched on.                                                                                                                                  |  |  |

| 1A37                 | CT133                   | DREADY, Device ready to transfer next output character. If<br>the device does not provide this signal, a U-link on the CU<br>must be positioned to hold this signal active within the CU. |  |  |

## 6.18 Echo Mode

Echo Mode is programmable by bit 10 in the R3 register associated with the CIO Start; this is indicated to the CU during CIO Start by D10 to the FECHO flip-flop. Each accepted INR command is memorized by the FACINR flip-flop. At T7 of the CPU ROM address 159, the active MUQ1 sets the CU flip-flop ECHO, and TDSN is validated up to T5 of the next cycle. The low level to the TDN input of the UART circuit causes the input data to be channelled back to the Data Out line to the device. The FACINR flip-flop remains set until the Wait Status state when it is reset by FNU from the CPU.

Figure 6-4 V24 Serial Control Unit Detailed Logic Diagram