## APPENDIX C MEMORY MANAGEMENT UNIT SERVICE MANUAL

.

·

÷

TABLE OF CONTENTS

Effective Pages

,

.

.

February 1977

,

## ii C.1 through C.19

4

## Paragraph

Figure

| C.1  | General                      | C -1  |

|------|------------------------------|-------|

| C.2  | Address Translation          | C -1  |

| C.3  | Page Usage Timer             | C -1  |

| C.4  | Memory Protection            | C - 2 |

| C.5  | Software Considerations      | C -2  |

| C.6  | System/User Operations       | C - 2 |

| C.11 | Page Replacement Facilities  | C - 3 |

| C.14 | Logic Description            | C - 5 |

| C.15 | Table Load                   | C -5  |

| C.19 | Table Store                  | C -6  |

| C.22 | WER Interval Time Loading    | C -7  |

| C.24 | Translation Operation        | C -7  |

| C.29 | Increment Timer              | C -9  |

| C.32 | Page Fault                   | C - 9 |

| C.35 | Input/Output Signals         | C -12 |

| C.36 | Circuit Board and Components | C -12 |

| C.37 | Address/Interrupt U-Links    | C -12 |

|      |                              |       |

## LIST OF ILLUSTRATIONS

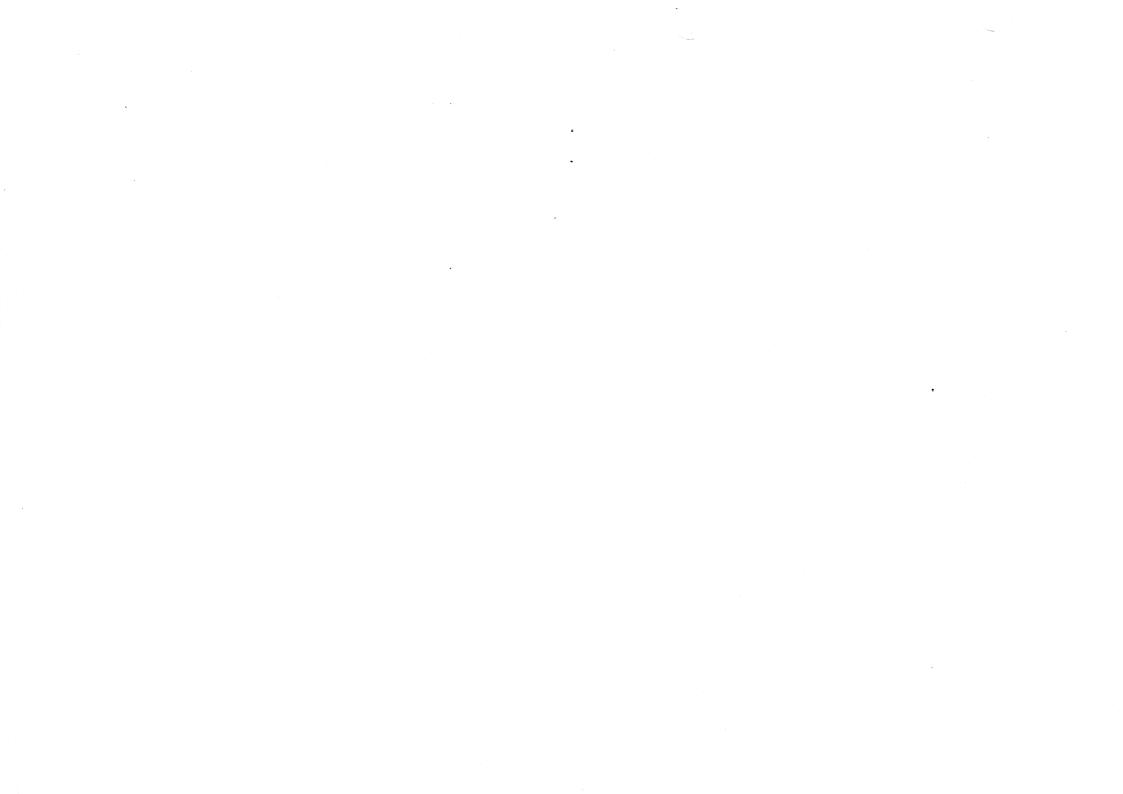

| C.1  | MMU System Diagram                                       | C - 3 |

|------|----------------------------------------------------------|-------|

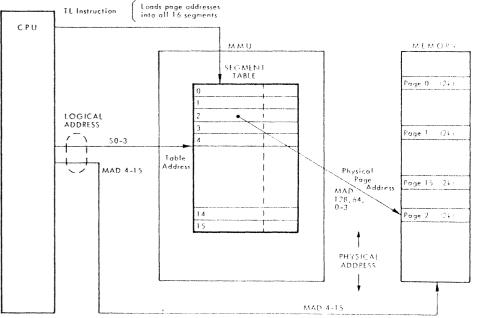

| C.2  | MMU Segment Table Contents                               | C - 4 |

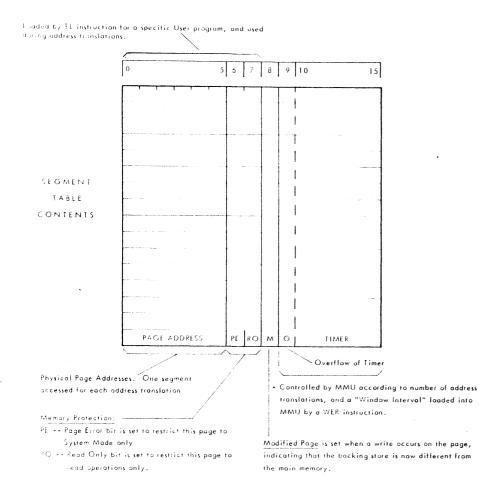

| С.3  | MMU Block Diagram                                        | C-4   |

| C.4  | Table Load Sequence                                      | C - 5 |

| C.5  | Table Store Sequence                                     | C - 6 |

| C.6  | WER Sequence (Loading Window Interval Software Constant) | C -7  |

| C.7  | Translation Sequences                                    | C - 8 |

| С,8  | Increment Timer Sequence                                 | C-10  |

| С.9  | Page Fault Sequence                                      | C -11 |

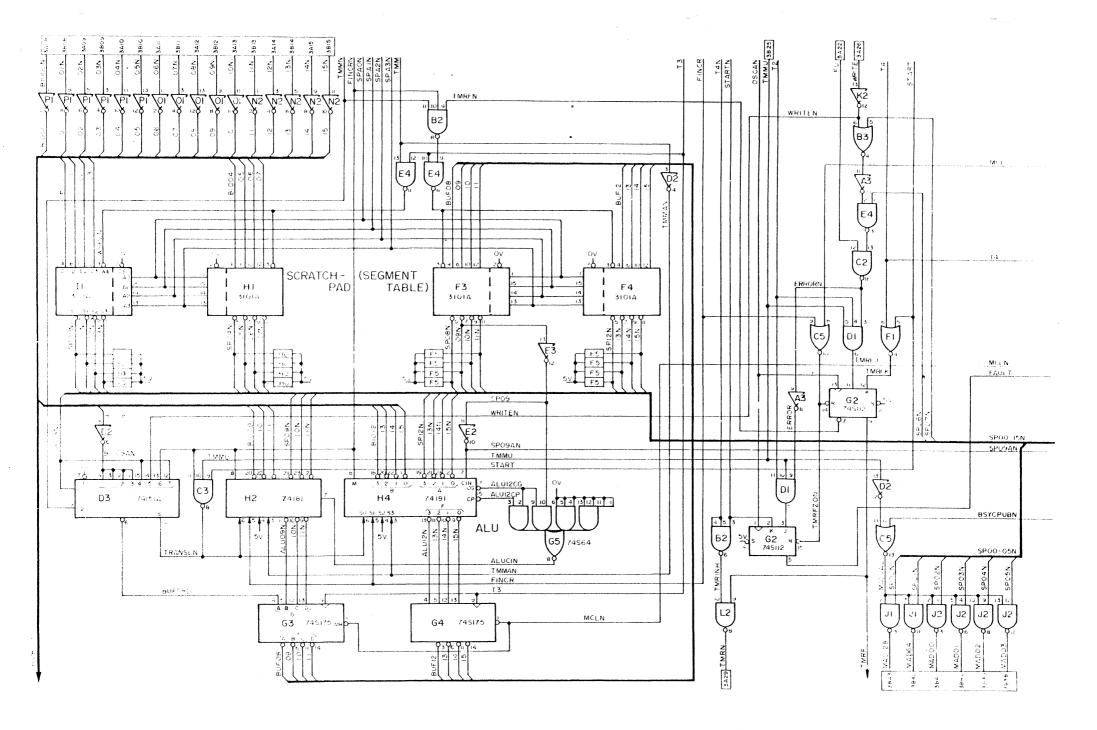

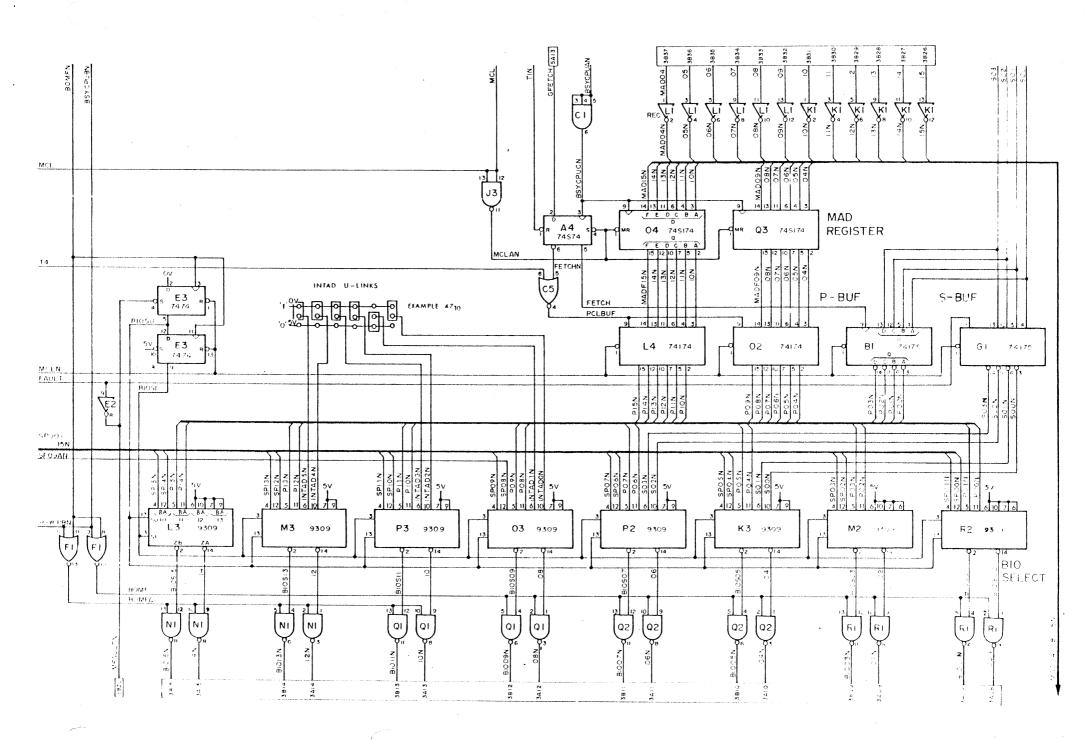

| C.10 | MMU Logic Diagram                                        | C-13  |

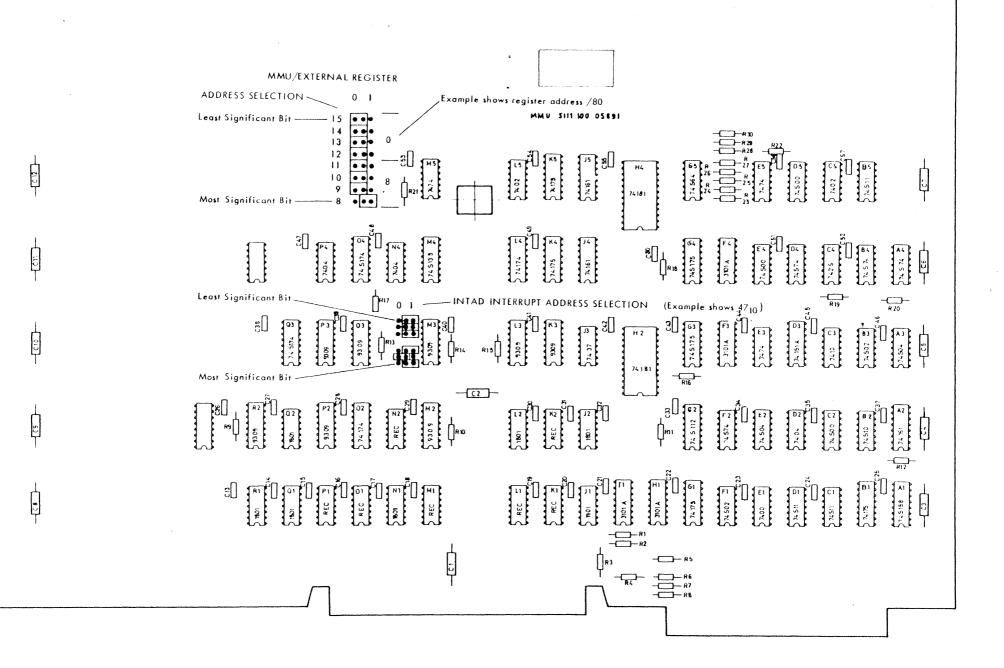

| C.11 | MMU Card Layout                                          | C -16 |

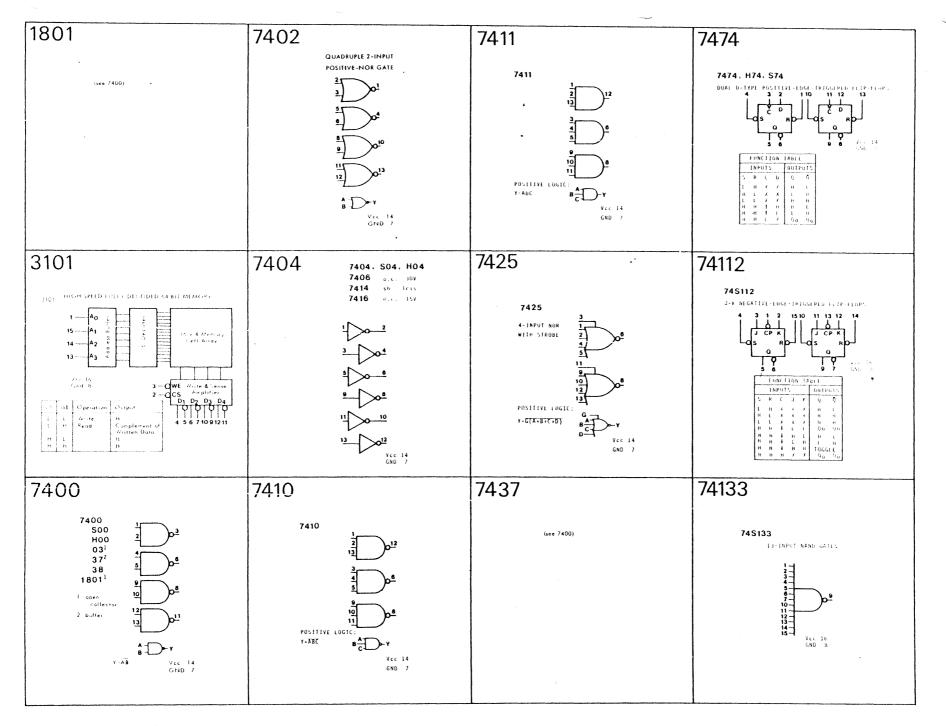

| C.12 | MMU IC Guide                                             | C-18  |

|      |                                                          |       |

## LIST OF TABLES

# TablePageC.1MMU Parts ListC-17

111

.

Page

Page

• •

#### APPENDIX C

#### MEMORY MANAGEMENT UNIT

#### C.I GENERAL

1 Page = 2 W words

The Memory Monagement Unit (MMU) is a hardware option which provides memory addressing and protection facilities for the P857 system. The MMU is a system slave which operates under CPU Bus control. The three main functions of the MMU are:

- Address translation which extends memory addressing up to 128k words.

- Page Usage Timing for dynamic program relocation on a page basis.

- Full memory protection.

#### C.2 Address Translation

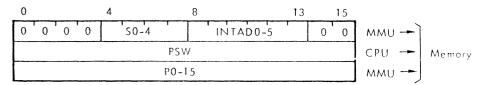

The primary function of the MMU is to extend memory addressing up to 128k physical words while retaining the 32k-word logical address selection from the CPU instruction (Figures C-1 and C-2).

- A sixteen-segment table is pre-loaded with page addresses by a single Table Load instruction.

- Each CPU/memory transfer via the MMU (MMU translation) then uses the four most-significant address lines (SO-3) to select a table segment, and thus a page address, while the 12 least-significant address bits select one of the 2k words within the page.

- A Table Store instruction can be used by software to access the 16-word segment table for testing or dynamic relocation.

#### C.3 Page Usage Timer

The function of the Page Usage Timer is to keep track of which pages have not been accessed within a certain Page Residency Parameter (Window Interval). This parameter

is based on the number of MMU translations and is derived from a software constant and an MMU hardware constant of  $1024 \ (2^{10})$ .

- An eight-bit (0-255) software constant is loaded into the MMU by a WER instruction. This interval time count is used as a software constant common to all 16 page timers.

- Each MMU translation resets the timer for the addressed page, and is counted as an "interval" time unit.

- Each time the interval count is complete, a single page timer (located in the MMU scratchpad) is incremented, and the next sequential page timer is selected in preparation for the succeeding page-timer count.

- A non-addressed page thus counts to overflow after a number of MMU translations equal to the software constant times the hardware constant 1024 (2<sup>10</sup>), as follows:

- -- Window interval (count 0-255).

- -- Sequential count through all 16 page timers (2<sup>4</sup>).

- -- Full six-bit page timer (2<sup>6</sup>).

#### C.4 Memory Protection

Each of the 16 words loaded into the segment table by the TL instruction includes, in addition to the page address, two memory-protection bits established by software.

- Bit 6 (E) -- The Page Error bit is set to restrict the page to System Mode. If an address translation in User Mode (FU set) attempts to access the page, the translation is blocked and MFAULTN is sent to the CPU.

- Bit 7 (R) -- The Read-Only Page bit is set to restrict the page to read operations only. If an address translation in User Mode attempts a write operation on this page, the translation is blocked and MFAULTN is sent to the CPU.

#### C.5 SOFTWARE CONSIDERATIONS

#### C.6 System/User Operations

The main memory is divided into a System part and a User part, with the System part always located at the beginning of the memory (lowest addresses). The System part contains the supervision programs (monitors) and their associated working areas (tables, buffers, etc.). The User part contains the user's running programs or real-time tasks, etc. The CPU operates in either System Mode or User Mode, and certain instructions are restricted to System Mode only.

C.7 The system part of memory is located in the beginning of memory and is "limited to the first 32k word positions. Addressing the System part of memory is done with the 16-bit logical address directly from the CPU, and the MMU is not used. However, the System is able to extend its addressing by using the extended instructions (EL, ES, MVSU, MVUS) which use MMU translation.

C.8 The maximum length of a single user program is 32k words, divided into pages of 2k words. The CPU addresses a user location with the 16-bit logical address. The MMU translates the first four bits into a six-bit physical page address (which was previously loaded into the MMU). The remaining 12 bits from the CPU then select one of 2k words within the selected page.

C.9 System mode instructions used by the MMU:

- Table Load (TL) loads 16 physical page addresses and protection bits from memory into the MMU segment table. This must be done prior to address translations through the MMU.

- Table Store (TS) stores the 16-word segment table (including page addresses, protection bits, and page timers) from the MMU into memory.

- Write External Register (WER) loads a Window-Interval software constant into the MMU for use with the page timers. The WER instruction is not exclusive to MMU operations.

Address translation is usually performed by the MMU while the CPU operates in User Mode, and the MMU does memory-protection checking. There are, however, four System-Mode instructions which are used for address translation operations:

- Extended Load (EL) and Extended Store (ES) are used by the System to access the User area of memory to read or write a single word.

- Move Table User-to-System (MVUS) and System-to-User (MVSU) are used by the System to transfer blocks of data between the User area of memory and the System area.

The only difference the MMU notices for these System-Mode address translation

operations is that the user-mode bit (FU) is not active, and the MMU does not do the memory-protection checking.

C.10 The Operating System must load the segment table every time a new User program is given control. The Operating System is also responsible for sending the 18-bit physical addresses of the User's 1/O buffers to the 1/O channels (1/O Processors or DMA controllers).

C.11 Page Replacement Facilities

.

C.12 Window Interval. The required window interval count (N) to obtain a specific page residency time (T) is: the time (T), divided by the average memory access time (<del>0</del>), divided by the hardware constant (1024).

T = 1024,  $\Theta$ , N or N = T  $\div \Theta \div 1024$

For example, if a page residency time of 100ms is desired and the average memory access time  $(\theta)$  is 2µsec, the window interval count (N) is:

100ms ÷ 2µsec ÷ 1024 = 50

Set into MMU by WER instruction.

Hardware constant (count through 16 timers of six bits each)

por case

Average memory access time: produces one count each time the MMU is accessed for address translation.

C.13 Modified Page. Bit M (08) is set by the MMU whenever a write operation (Store instruction) is performed on a specific page. This feature indicates to the Operating System when a page needs to be swapped out before a new program segment is loaded at the same place. If not necessary, a direct over-writing is possible, resulting in a large saving of time.

WORD CHAR Address within selected pour

C-4 REV.1 Figure C-2 MMU Segment Table Contents

#### C.14 LOGIC DESCRIPTION

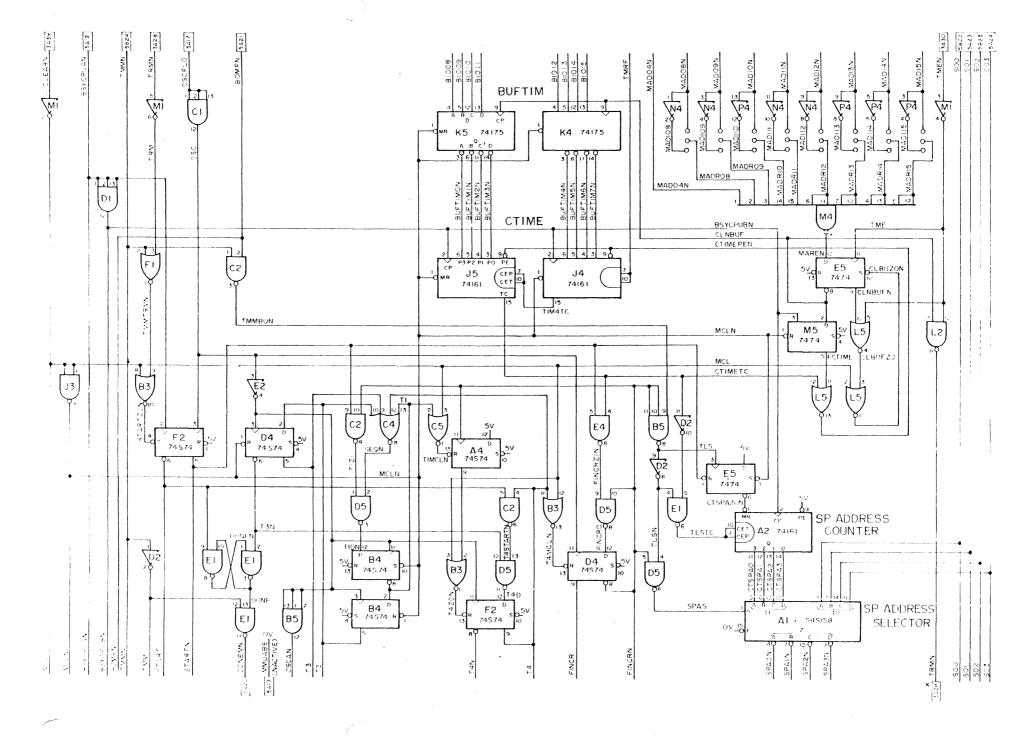

The MMU logic description is organized into the different operating sequences of the MMU. A general block diagram of the MMU is provided in Figure C-3. The detailed logic is shown in Figure C-10 at the end the logic description. The different operating sequences used in the MMU are:

- Table Load

- Table Store

- WER -- Interval Time Loading

- Translation Operation

- Increment Timer

- Page Fault

#### C.15 Table Load

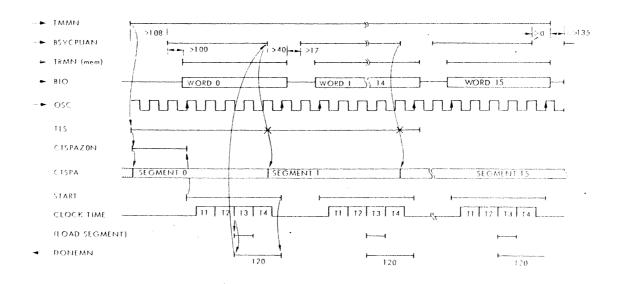

The CPU starts the Table Load operation (Figure C-4) in the MMU by sending TMMN. The CPU controls the operation with the signal BSYCPUAN which it sends for each of the 16 page addresses to be loaded into the MMU segment table. TRMN is received from the memory each time the data from the memory is valid. The TMMN signal resets counter CTSPA (via TLS and CTSPAZON) so that segmenttable position 0 is selected for the first entry. The active signal TLSN enables CTSPA counting and selects the counter input to the SP-Address Selector with a high SPAS.

C.16 When the memory is ready with the data, TRMN goes active and removes the reset clamp STARTZON from the START flip-flop. The following high transition of OSC then sets START. The MMU clock T1, T2, T3, T4 runs when START is set, synchronized on OSC from the CPU. One word with the page address and memoryprotection information is gated from BIO into the segment table at time T3. Also at T3, DONEMN is sent to the CPU to request the next word transfer.

C.17 Next Word Transfer. The CPU responds to DONEMN by dropping BSYCPUAN. The MMU increments the CTSPA count at the trailing edge of BSYCPUAN to select the next position in the segment table. START resets on the first rising OSC after BSYCPUAN drops, and is held reset when TRMN goes inactive. When memory is ready with data, TRMN goes active and the MMU

BE7

sequence (START, clock cycle, BIO + segment table, DONEMN) is repeated to load this word.

C.18 Last Word Transfer. The CPU drops TMMN after it receives the 16th DONEMN from the MMU. The inactive TMM signal in the MMU blocks further sending of DONEMN to the CPU. In all other respects, the MMU sequence for the last word transfer is identical to the previous transfers.

#### C.19 Table Store

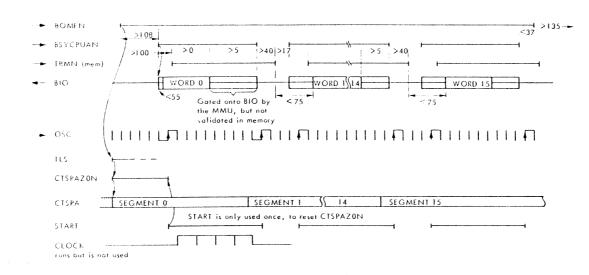

The CPU starts the Table Store operation (Figure C-5) in the MMU by sending BOMFN. The CPU controls the operation with the signal BSYCPUAN which it sends for each of the 16 segment-table words to be transferred out to memory. TRMN is received from the memory each time the BIO data from the MMU has been accepted. The CPU uses TRMN to know when to initiate each transfer. The BOMFN signal resets counter CTSPA (via TLS and CTSPAZON) so that segment table position 0 is selected for the first entry. The active signal TLSN enables CTSPA counting and selects the counter input to the SP-Address Selector with a high SPAS.

C:20 The MMU uses BSYCPUAN and BOMEN to gate the first segment-table word (including page address, memory protection, and page timer information) onto the BIO to the memory. When the memory has accepted the data, TRMN goes active and removes the reset clamp STARTZON from the START flip-flop. The following high transition of OSC then sets START. The START signal resets CTSPAZON to allow the CTSPA counter to increment at each trailing edge of BSYCPUAN. START and the MMU clock continue to operate with each BSYCPUAN input, but are not used for the rest of the Table Store operation.

C.21 Each successive word is gated from the MMU segment table onto the BIO lines by the BSYCPUAN signal. The trailing edge of BSYCPUAN increments CTSPA to select the words sequentially from the segment table. The CPU terminates the operation after the 16th word transfer by dropping the BOMEN signal.

NOTES: • Times in ns.

OSC signal is not complete; shows only the relationship between edges of BSYCPUAN and OSC, for controlling START and clock times. C.22 WER -- Interval Time Loading

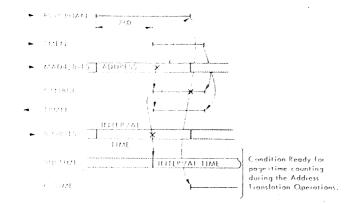

The CPU loads the window interval software constant into the MMU with a WER instruction (Figure C-6). The CPU starts the operation by activating BSYCPUAN and, at the same time, placing the MMU address on the MAD08-15 lines and placing the window interval software constant on the BIO08-15 lines. When the MMU decoder logic detects its own address on the MAD lines and the WER instruction code (MAD04 = 0), signal MAREN is activated. With decoded-address signal MAREN active, the CPU timing signal TMEN sets flip-flop CLNBUF. The CLNBUE output gates the interval time from the BIO lines into the BUFTIME register and also, in conjunction with TMEN, generates the timing response signal TRMN back to the CPU.

C.23 The CPU responds to TRMN by terminating BSYCPUAN to the MMU. The trailing edge of BSYCPUAN, gated by CLNBUF, sets the FCTIME flip-flop. With FCTIME set and the interval time loaded in the BUFTIME register, the MMU is ready for page-time counting during the address-translation operations. When the CPU drops TMEN, the MMU resets CLNBUF (via CLBUFZO, CLBUFZON) and drops the TRMN signal to the CPU.

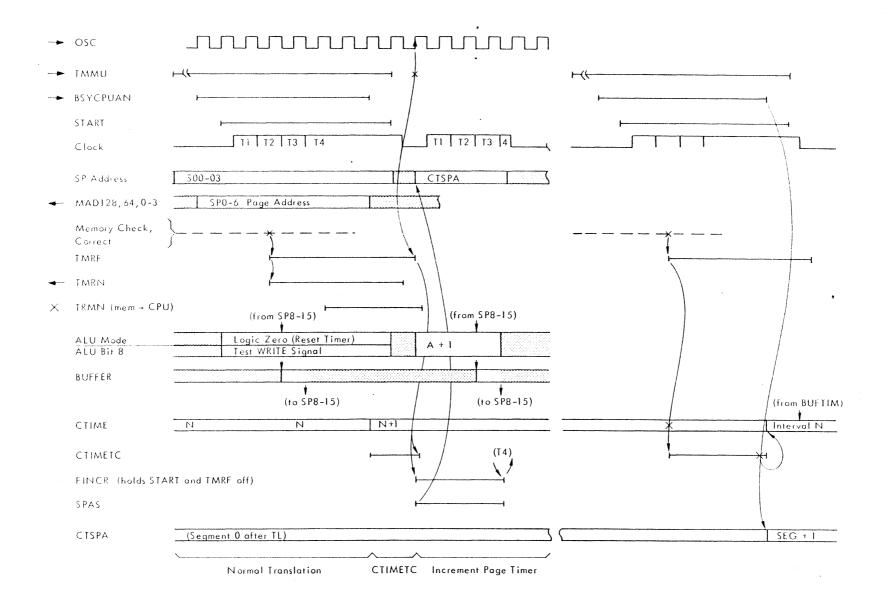

C.24 Translation Operation

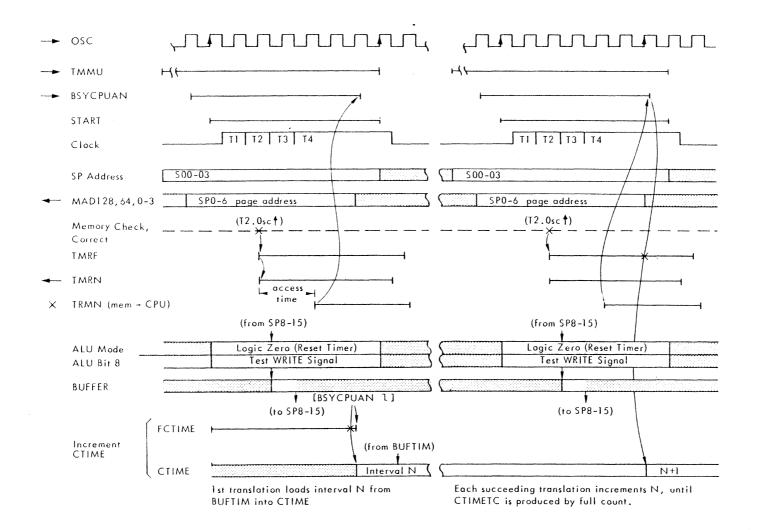

The CPU activates signal TMMU to indicate a memory transfer requiring MMU address translation (Figure C-7). The MMU scratchpad address selector is switched to the S00-03 input by the inactive SPAS (FINCRN.TLSN). TMMU and BSYCPUAN together gate the physical page address (SP00-05) from the location selected by the logical page address (S00-03).

C.25 The START flip-flop is set on the first rising edge of OSC after BSYCPUAN is received. Each trailing edge of OSC then increments the MMU clock. The signals TMMU.START.FINCRN (=TRANSL) set the BUF08D selector to test the WRITE signal from the CPU. TRANSLN, together with TMMN.FINCR, sets the ALU to the Logical-Zero' mode (FINCRN to the Mode input pin 8 selects Logical operations). The leading edge of T3 gates the addressed-word timer from SP08-15, through the ALU, to the Buffer: this resets the timer (bits 09-15) and sets bit 8 if the operation is a Write operation. The Buffer contents are reloaded into SP08-15 at the trailing edge of T3.

C.26 When the SP word is accessed by S00-03, the bits 6 and 7 are compared with the CPU command bits FU and WRITE. If bit 6 is set and FU is active (System Mode only bit and User Mode), ERRORN is generated. If bit 7 is set and WRITE is active (Read-Only bit and Write command) and FU is set (User Mode), ERRORN is generated and MFAULTN is sent to the CPU. This error condition prevents setting TMRF at T2, and blocks the sending of TMRF to memory, thus blocking the memory transfer.

C.27 If the memory check is correct, the TMRF flip-flop is set at T2 by the rising edge of OSC. TMRF and START together send timing signal TMRN to the memory. When the memory part of the transfer is complete, it sends TRMN to the CPU. The CPU responds by dropping BSYCPUAN to the MMU.

C.28 During the first translation operation following a WER instruction, flip-flop FCTIME is set. When BSYCPUAN drops at the end of the first translation, the complement of the software constant is gated from the BUFTIM

Ú.

register into the CTIME counter. When BSYCPUAN drops at the end of all succeeding translations, CTIME is incremented.

#### C.29 Increment Timer

The complement of the software constant is loaded into CTIME from the BUFTIM register (Figure C-8). Each translation increments CTIME so that it will be full when the number of translations equals the software constant. When the trailing edge of BSYCPUAN increments CTIME to full, CTIMETC is produced. The next rising edge of OSC then sets flip-flop FINCR. The same edge of OSC also resets TMRF (normal translation sequence). With TMRF removed from the CET input of CTIME, the CTIMETC output drops.

C.30 The FINCR flip-flop activates SPAS so that the scratchpad address selector selects the CTSPA source. The active FINCR signal also sets the ALU and the BUF08D selector to the arithmetic A+1 mode. At the leading edge of time T3, the scratchpad page timer (bits 08-15) selected by CTSPA is gated through the ALU into the BUFFER. At the trailing edge of T3, the buffer contents are loaded back into the scratchpad, now incremented by 1. FINCR is reset by the T4 clock, and the inactive FINCR signal then resets T4 to end the increment timer sequence.

C.31 TMRF is generated during the succeeding translation sequence and, since CTIME still contains its full count, the CTIME output is reactivated. At the end of the translation then, CTIMETC causes the trailing edge of BSYCPUAN to increment the CTSPA counter (for selecting the next page timer) and to reload the CTIME counter with the complement of the software constant from the BUFTIM register.

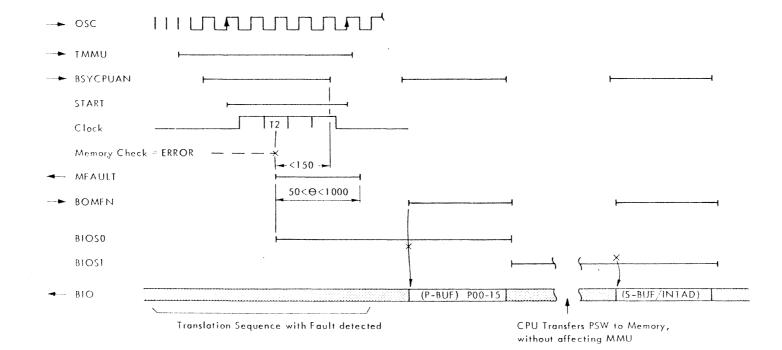

#### C.32 Page Fault

A page fault is detected during a normal Translation sequence if a User Mode operation (FU set) accesses a System-Mode-only page (bit 6 set) or if a Write operation is attempted (WRITE signal) in User mode on a read-only page (bit 7 set). The resultant ERROR signal inhibits the TMRF flip-flop and blocks the sending of the memory timing signal TMRN. The flip-flop FAULT is set at time T2 (Figure C-9). FAULT generates the MFAULTN signal to the CPU, gates the S00-03 bits into the S-Buf register, and sets the BIOSO flip-flop.

C.33 BIOSO and BIOSI are now set (=1,0) to select the P-Buf source via the BIO Select circuit. The CPU responds to MFAULT by sending BOMFN and BSYCPUAN to the MMU. These two signals together gate the P-Buf contents (P00-15) onto the BIO lines to the CPU. At the trailing edge of BOMFN, BIOSO is reset and BIOSI is set (=0,1) so they select the S-Buf and INTAD sources via the BIO Select circuit. The next time BSYCPUAN and BOMFN are received together from the CPU, the MMU gates the segment-table address (S00-03) and the MMU interrupt code (INTAD0-5) onto the BIO lines.

C.34 The CPU activates BSYCPUAN once between the two BOMEN signals to transfer its PSW to memory. Since BOMEN is not active, however, there is no action taken in the MMU at that time.

Stack after Page Fault Interrupt

S = page number

P = program counter or aborted instruction

.

4

#### C.35 INPUT/OUTPUT SIGNALS

| CPU - MMU S       | CPU - MMU Signals                                                                                                                                                                                                                                          |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BSYCPUAN          | CPU has Bus control. Validates Bus signals and controls all MMU operations.                                                                                                                                                                                |  |  |

| BOMEN             | Table Store control signal.<br>Page-fault stack-loading control signal:<br>1st to read aborted instruction-counter value;<br>2nd to read logic page address which set page fault and<br>the program level of the page-fault job, coded on the<br>MMU card. |  |  |

| FU ≈ 1<br>≈ 0     | CPU in User Mode. Any memory violation sets page fault.<br>CPU in System Mode.                                                                                                                                                                             |  |  |

| GFETCH            | Fetch cycle is executed by CPU. Instruction counter value is loaded into MMU P-Buf register.                                                                                                                                                               |  |  |

| OSCFLO            | CPU clock signal, used by MMU for internal timing.                                                                                                                                                                                                         |  |  |

| S00-03            | Logical page address from CPU P-register.                                                                                                                                                                                                                  |  |  |

| TMMN              | Table Load control signal.                                                                                                                                                                                                                                 |  |  |

| тмми              | Translation control signal; for page-address translation, memory protection check, and memory activation by the MMU.                                                                                                                                       |  |  |

| MMU ~ CPU Signals |                                                                                                                                                                                                                                                            |  |  |

| DONEMN            | MMU reply during Table Load as each segment is loaded.                                                                                                                                                                                                     |  |  |

| MFAULTN           | Page fault is detected during translation.                                                                                                                                                                                                                 |  |  |

| MMUABS            | Held at 0v (inactive) when MMU card is in place.                                                                                                                                                                                                           |  |  |

| BUS - MMU Signals |                                                                                                                                                                                                                                                            |  |  |

| BIO0N-15N         | Data used during Table Load and WER operations.                                                                                                                                                                                                            |  |  |

| CLEARN            | Clear signal for initializing system.                                                                                                                                                                                                                      |  |  |

| TMEN              | WER instruction timing for loading the software constant into the MMU BUFTIM register.                                                                                                                                                                     |  |  |

| TRMN              | Memory reply:<br>During Table Load and Table Store validates data.<br>During translation releases memory activation.                                                                                                                                       |  |  |

| MAD04-15          | Address lines to:<br>select the MMU during WER instruction, and<br>store the CPU instruction-counter value during each Fetch<br>instruction cycle.                                                                                                         |  |  |

| WRITE             | CPU command for store cycles. Used during translation to test<br>for page fault (read-only page and User Mode), and sets segment<br>table Modified-Page bit (8) of accessed page (if no page fault).                                                       |  |  |

| MMU + BUS Signals |                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------|

| BIO0N-15N         | Data used during Table Store or Page-Fault stack loading operations.                    |

| MAD128,64,<br>0-3 |                                                                                         |

| 0-3               | Memory address lines for physical page addresses from the segment table.                |

| TMRN              | Activates memory during page address translation, if there is no page fault.            |

| TRMN              | External register reply to CPU when software constant is loaded during WER instruction. |

## C.36 CIRCUIT BOARD AND COMPONENTS

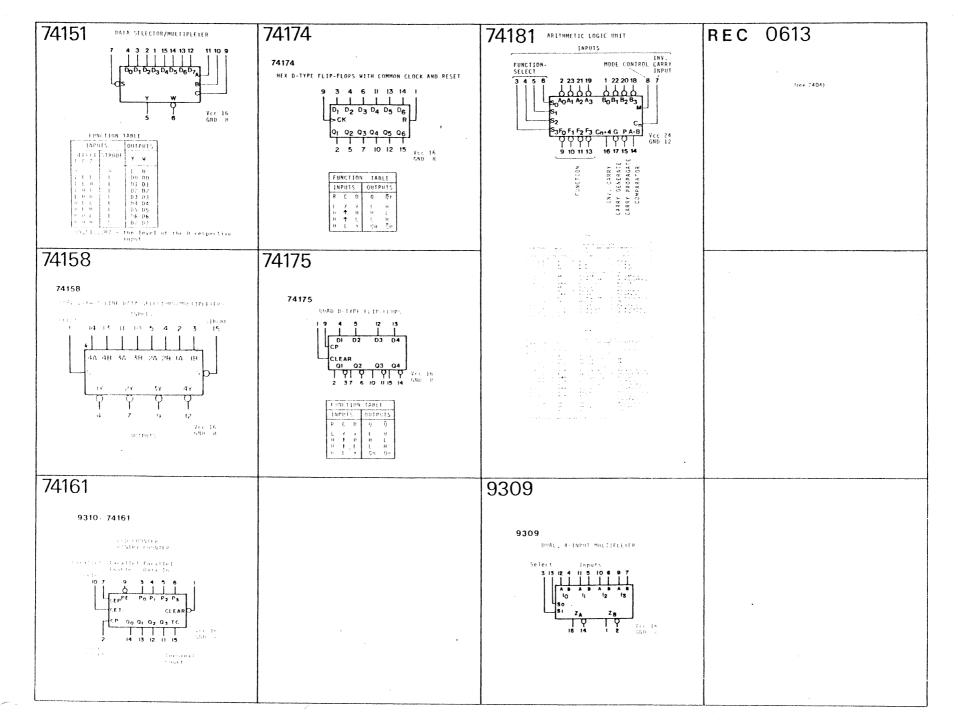

The Memory Management Unit is implemented on a double-sided printed circuit board. Component locations are shown on Figure C-11. The MMU uses connector 3 for GP Bus connections and power, and connector 5 for special CPU control signals. The MMU parts list is given in Table C-1. A list and guide of the integrated circuits used by the MMU is provided in Figure C-12.

## C.37 ADDRESS/INTERRUPT U-LINKS

The U-link connections for both the external-register address of the MMU and the interrupt level address are shown on Figure C-11. For both groups of U-links, the least-significant bits are at the top and the most-significant are at the bottom. The examples shown on Figure C-11 are set up for the standard external-register address and standard interrupt level of the MMU (address /80 and level  $47_{10}$ ).

5NT/2F DA 180

(=47 ...)

Figure C-10c MMU Logic Diagram

REV

#### Table C-1 MMU Parts List

| Reference                | Description                   | 12NC Code      |

|--------------------------|-------------------------------|----------------|

|                          | Printed circuit               | 5111 100 05891 |

| A1                       | Integrated circuit 745158     |                |

| BE G1 K4 K5.             | Integrated circuit 74175      |                |

| 85 C1 D1,                | Integrated circuit 74511      |                |

| E1.                      | Integrated circuit 7400       |                |

| 83 FT.                   | Integrated circuit 74502      |                |

| 13 F4 H1 H.              | Integrated circuit 3101A      |                |

| 11 J2 U2 N1 Q1 Q2 R1.    | Integrated circuit 1801       |                |

| FT K2 LI MI N2 OI PL.    | Integrated circuit REC 0613   |                |

| A2 J4 J5.                | Integrated circuit 74161      |                |

| 82.                      | Integrated circuit 74510      |                |

| C2 D5 E4                 | Integrated circuit 74500      |                |

| D2 N4 P4.                | Integrated circuit 7404       |                |

| A3 E2                    | Integrated circuit 74504      |                |

| A4 B4 D4 F2              | Integrated circuit 74574      |                |

| G2 <sup>•</sup>          | Integrated circuit 745112     |                |

| H2 H4                    | Integrated circuit 74181      |                |

| F3 L3 M2 M3 O3 P2 P3 R2. | Integrated circuit 9309       |                |

| 14 02.                   | Integrated circuit 74174      |                |

| C3.                      | Integrated circuit 7410       |                |

| €4.                      | Integrated circuit 7425       |                |

| C5 t5.                   | Integrated circuit 7402       |                |

| D3.                      | Integrated circuit 74151A     |                |

| E3 E5 145.               | Integrated circuit 7474       |                |

| G3 G4.                   | Integrated circuit 74\$175    |                |

| 65.                      | Integrated circuit 74564      |                |

| 13.                      | Integrated circuit 7437       |                |

| M4,                      | Integrated circuit 745133     |                |

| O4 Q3.                   | Integrated circuit 745174     |                |

| F9-22                    | Resistor 1Kn, 0.25W, 5%.      |                |

| F1-8,23-30.              | Resistor 560n, 0.25W, 5%.     |                |

| <1.2.                    | Capacitor 47µF, 10V, FIICO.   |                |

| < 3 - 12                 | Capacitor 10µF, 25V, FIICO.   |                |

| 13-35,37-57,             | Capacitor 10nF, 20%, ceramic, |                |

|                          | U Link DCW 06                 |                |

.

C -17

.

Figure C-12b MMULIC Calib

1 - 1 - 5 N

## APPENDIX D

## FLOATING POINT PROCESSOR

.

ie.

#### SERVICE MANUAL

## Effective Pages

.

.

March 1977

~~~~

,

## TABLE OF CONTENTS

ii through iv D.1 through D-28

4

| Paragraph |                                | Page  |

|-----------|--------------------------------|-------|

| D.1       | General                        | D -1  |

| D.2       | Logic Layout                   | D -1  |

| D.4       | Instructions                   | D -3  |

| D.5       | Data Format                    | D-3   |

| D.6       | Floating-Point Data            | D - 3 |

| D.11      | Integer Data                   | D-3   |

| D.12      | Operational Flow               | D-5   |

| D.14      | Start of Commands              | D -5  |

| D.15      | FFL Command                    | D -5  |

| D.17      | FFX Command                    | D-9   |

| D.19      | FLD Command                    | D -9  |

| D.20      | FST Command                    | D-9   |

| D.21      | FAD, FSU Commands              | D - 9 |

| D.22      | FMU Command                    | D - 9 |

| D.23      | FDV Command                    | D-10  |

| D.24      | Logic and Timing               | D-10  |

| D.25      | Microprogram Control (logic c) | D-10  |

| D.28      | Sequensor (logic d)            | D-13  |

| D.30      | Instruction Loading (logic d)  | D-13  |

| D.31      | Operand Loading                | D-13  |

| D.33      | Store Operand                  | D-13  |

| D.34      | FPP Operation Control          | D-13  |

| D.35      | Status and Interrupts          | D-17  |

| D.38      | Signal List                    | D-18  |

| D.39      | Card Layout                    | D-18  |

| D.40      | Parts List                     | D -18 |

## LIST OF ILLUSTRATIONS

.

| Figure |                             | Page   |

|--------|-----------------------------|--------|

| D.1    | FPP Block Diagram           | D -2   |

| D.2    | FPP Instructions            | D -4   |

| D.3    | Format and Range of Numbers | D - 5  |

| D.4    | FPP Flow Diagram            | D-6    |

| D.5    | FPP Timing                  | D -1 4 |

| D.6    | Logic Control Codes .       | D -1 5 |

| D.7    | FPP Logic Diagram           | D-19   |

| D.8    | FPP Card Layout             | D -24  |

| D.9    | FPP IC Guide                | D-26   |

## LIST OF TABLES

| D.1Next Address Branch ConditionsD-7D.2Address ROM (RAD) ListingD-8D.3Microprogram (ROM) ListingD-11 |  |

|------------------------------------------------------------------------------------------------------|--|

| · · · · · · · · · · · · · · · · · · ·                                                                |  |

| D.3 Microprogram (ROM) Listing D-11                                                                  |  |

|                                                                                                      |  |

| D.4 FPP Signal List D-18                                                                             |  |

| D.5 FPP Parts List D-25                                                                              |  |