Data Systems

Service Manual

# P800M Interface and Installation Manual

Preliminary

I

A PUBLICATION OF PHILIPS DATA SYSTEMS APELDOORN, THE NETHERLANDS.

PUB. NO. 5122 991 26942

DATE April 1976

Great care has been taken to ensure that the information contained in this handbook is accurate and complete. Should any errors or omissions be discovered, however, or should any user wish to make a suggestion for improving this handbook, he is invited to send the relevant details to:

PHILIPS DATA SYSTEMS SERV. DOC. AND TRAINING DEPT. P.O. BOX 245, APELDOORN, THE NETHERLANDS.

Copyright (c) by PHILIPS DATA SYSTEMS. All rights strictly reserved. Reproduction or issue to third parties in any form whatever is not permitted without written authority from the publisher. This Interface and Installation Manual is provided to aid a user wishing either to extend or modify an existing minicomputer system in the P800M family (P852M,P856M,or P857M),or to connect non-standard peripheral equipment to a system,or to integrate a P852M,P856M,or P857M into his own data processing system.

The manual provides technical data-such as functions, levels, and timings-for signals at the CPU General Purpose Bus and other interfaces, including interrupt and break request connections. It also describes, in general terms, the operation of the CPU when using programmed channel, I/O processor channel, or DMA controllers and gives examples of data exchanges which can take place.

A general description of control unit operation and I/O interface logic is given and information is provided to aid a user wishing to construct his own control units on printed wiring boards. Full details of all standard control units can be found in the appropriate manuals listed in the Appendix.

Section 2 of the manual provides installation information. The compact, yet versatile, nature of the P800M range creates no special difficulties for installation but the system possibilities are so diverse that it is not practical to give specific instructions on how to install each particular system configuration. Therefore information is given about the standard items of equipment available, to enable a suitable system arrangement to be determined and installed, and also general installation details which, it is considered, would be of use when installing any of the possible configurations. Reference should also be made to the documents issued by the peripheral equipment suppliers and to the other relevant manuals listed in the Appendix.

Great care has been taken to ensure that the information contained in this manual is accurate and complete. However, should a user find any errors or omissions, or wish to suggest improvements, he is invited to write his comments on the sheet provided at the end of the manual and send it to:

MANUAL WRITING SMALL COMPUTERS at the address on the opposite page.

`

|                                    |   |   |   |   | api | le c | T | Conten |

|------------------------------------|---|---|---|---|-----|------|---|--------|

|                                    |   |   |   |   |     |      |   | Page   |

| Preface                            | • | • | ٠ | • | •   | •    | ٠ | III    |

| List of illustrations              | • | ٠ | • | • | ٠   | •    | • | Х      |

| List of Tables                     | • |   | ٠ | ٠ | ٠   | •    | ٠ | XIII   |

| Summary                            | • | ٠ | • | ٠ | ÷   | 0    | e | XIV    |

| Definitions and Abbreviations .    |   | ٠ | • | 0 | ٠   | 5    |   | XVI    |

| SECTION 1 - INTERFACING            |   |   |   |   |     |      |   |        |

| PART 1 INPUT/OUTPUT ORGANISATION   | • |   | ø | • | ¢   | •    |   | 1-1    |

| Chapter 1 General Description .    |   |   |   | • | •   | •    |   | 1-3    |

| Data Handling Unit P852M           | • | • | • | • | •   | •    | • | 1-4    |

| Data Handling Unit P856M/P857M .   | ٠ | • |   | • | •   | •    |   | 1-8    |

| Memory Management Unit (P857M) .   | • | • | • | • | •   | •    | • | 1-11   |

| Extra Facilities (P856M and P857M) | • | • | • | • | •   | •    | • | 1-12   |

| Memory Interleaving                | ٠ | • | • | e | •   | •    | 6 | 1-12   |

| Micro-diagnostics                  | • | • | • |   | •   | ٠    | • | 1-12   |

| Extended Control Panel             |   | • | 6 | ۰ | ٠   |      | • | 1-12   |

| Input/Output Channels              | • | • | ۰ | 4 | •   | ٠    | • | 1-13   |

| General Purpose Bus                | 0 |   | • | ٠ | ٠   | •    | • | 1-13   |

| Master Slave Relationship          | ø | e | ٠ | • | •   | •    | • | 1-14   |

| Priority Structure                 | • | • | ٠ | • | •   | •    | • | 1-14   |

| External Connection                |   | • | • |   | •   | ٠    | • | 1-14   |

| Standard Control Units             | • | • | ۰ | • | •   | ٠    | • | 1-14   |

| User Designed Control Units .      | G | • | ٠ | ٠ | ę   | 8    | • | 1-16   |

| Control Unit Operation             | ¢ | • | ¢ | • |     | ٠    | ٠ | 1-16   |

| Interrupt System                   | • | • | • | • | •   | ٠    |   | 1-16   |

| Internal Interrupts                | e | ٠ | • | • | •   | ٠    |   | 1-17   |

| Timing Control Signals             | ٠ | 9 | • | ۰ | ٠   | •    | ٠ | 1-18   |

| Chapter 2 General Purpose Bus .    | ٥ | ۰ | • | 0 | 8   | 9    | • | 1-19   |

| GP Bus Signals                     | • | • | • | • | ٠   | •    | ٠ | 1-19   |

| Chapter 3 Programmed Channel       |   | • | e | ٠ | •   | ٠    | • | 1-24   |

| I/O Instructions                   | ٠ | ٠ | ٠ |   | ٠   | •    | • | 1-27   |

| Programming                        | • | ٠ | • | e | •   | •    | • | 1-27   |

| I/O Processor and DMA Role         | • | • | ٠ | • | ٠   | ٠    |   | 1-28   |

|                                    |   |   |   |   |     |      |   |        |

|                                                          |    | Page          |

|----------------------------------------------------------|----|---------------|

| Exchange Timings                                         | ٠  | 1-28          |

| Exchanges - Write External Register and Write in Memor   | у  | 1-29          |

| Exchange - Read External Register or Memory              | ٥  | 1-32          |

| Exchange - Master to Control Unit                        |    | 1-34          |

| Exchange - Control Unit to Master                        | •  | 1-35          |

| Guard Times                                              |    | 1-41          |

| Chapter 4 I/O Processor Channel                          |    | 1-43          |

| Operation                                                |    | 1-43          |

| Initialization Operation                                 | •  | 1-45          |

| Exchange Operation                                       |    | 1 <b>-</b> 46 |

| End of Block Transfer                                    | •  | 1-47          |

| Exchange of Variable Length Blocks                       |    | 1-50          |

| Relationship between Break Signal and Control Unit Addre | ss | 1-50          |

| System Organization Rules                                |    | 1-51          |

| Programming                                              | •  | 1-51          |

| Performance                                              | •  | 1 <b>-</b> 51 |

|                                                          | •  | 1- )1         |

| Chapter 5 Priority Structure                             | ۰  | 1-53          |

| CPU Priority                                             | ٠  | 1-53          |

| Bus Allocation System                                    | ٠  | 1-53          |

| System Operation                                         | ۰  | 1-55          |

| Timing of the Priority Chain                             | 6  | 1 <b>-</b> 57 |

| Overall Performance                                      | ٠  | <b>1-</b> 58  |

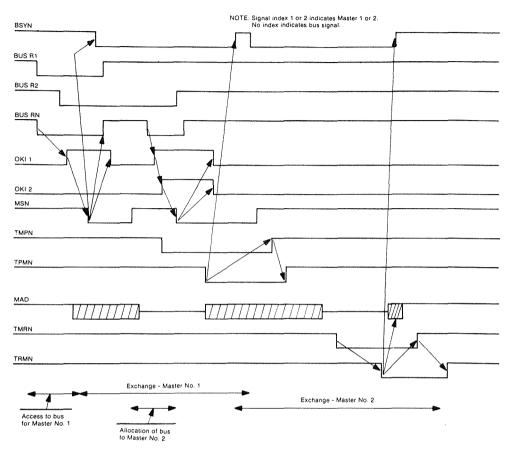

| Chaining of the Exchange                                 | ٠  | 1-58          |

| Chapter 6 Interrupt System                               | •  | 1-61          |

| Interrupt System                                         | ٥  | 1-61          |

| Interrupt Handling                                       | •  | 1-63          |

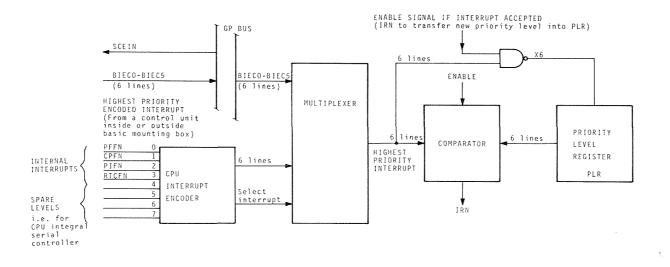

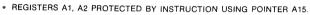

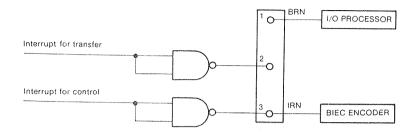

| Interrupt Signal Encoding for a System                   |    | 1-65          |

| Interrupt Selection on BIECO-5 Lines                     |    | 1-66          |

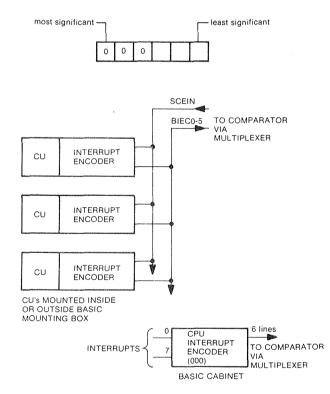

| Timing of SCEIN Signal                                   |    | 1-67          |

| Chapter 7 Digital Input/Output Sugton (DIOG)             |    |               |

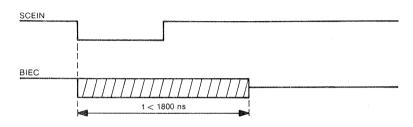

| Chapter 7 Digital Input/Output System (DIOS)             | ٠  | 1-69          |

| Configurations                                           | ٠  | 1-69          |

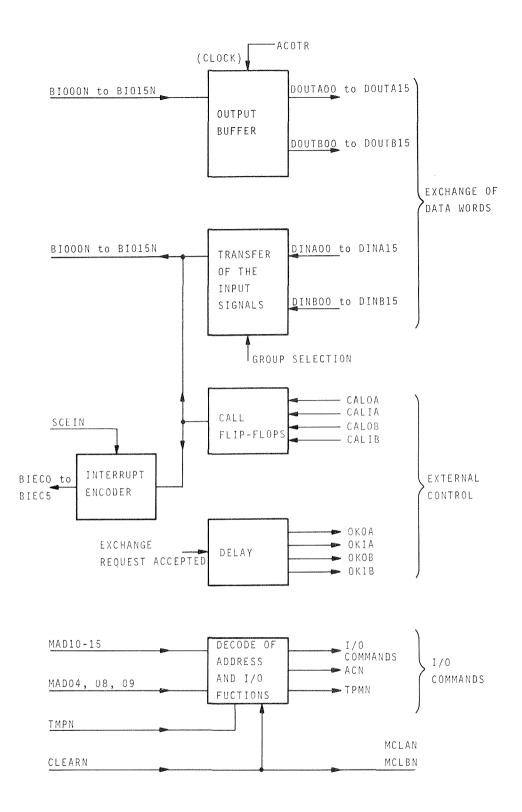

| Signals between DIOD Board and CPU                       | ٠  | 1-69          |

| Signals between device and DIOD board                    | •  | 1-71          |

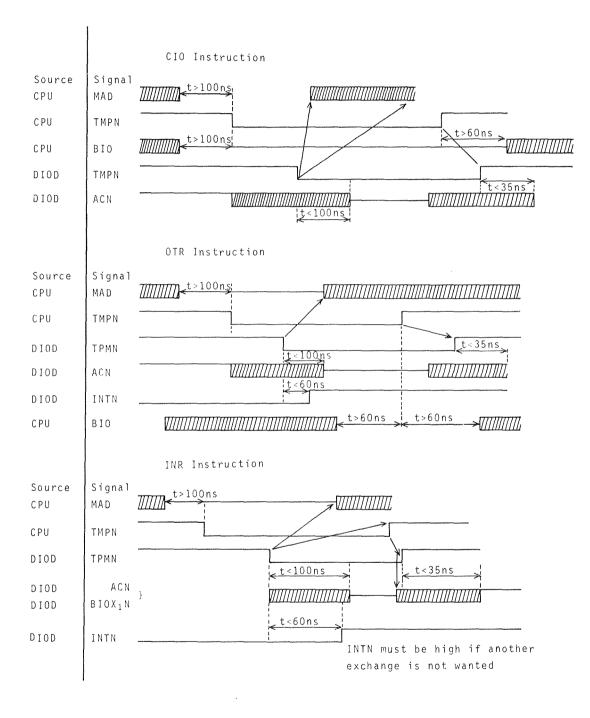

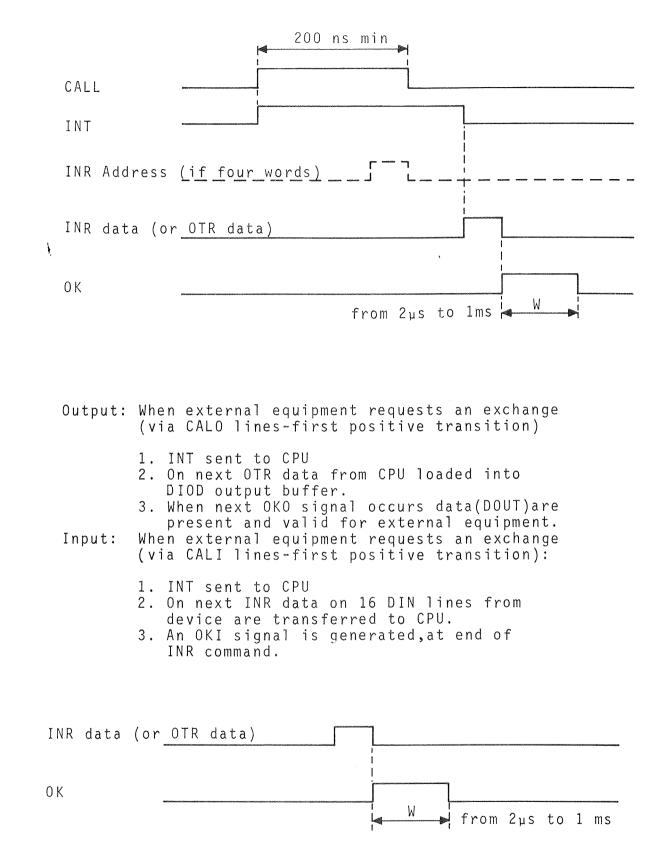

| Operation                                                | ٠  | 1-71          |

| Initiation by a Call signal                              | •  | 1-73          |

| Initiation by Software                                   | •  | 1-75          |

|                                      |                   |                  |                  | Page                        |

|--------------------------------------|-------------------|------------------|------------------|-----------------------------|

| Timing for Control Lines             | 8 8 C             | 6 6              | 8 e -            | • 1-75                      |

| Sequences                            | • • •             | \$ <del>\$</del> | 8 8 ·            | • 1-77                      |

| Start Mode or Stop Mode              | e e g             | e 6              | e e .            | . 1-77                      |

|                                      |                   |                  |                  |                             |

| PART 2 INTERFACE CIRCUITS AND HARD   | WARE .            | 0 6              | 8 <b>9</b>       | • 2-1                       |

| Chapter 1 Introduction               | 6 6 e             | 0 G              | 0 0              | . 2-3                       |

| Basic Mounting Boxes M1. M2, M4, M   |                   |                  |                  | 0 7                         |

|                                      | Sh                | elves E´         | I and E2         | 2-3                         |

| Printed Wiring Boards                | 8 G 6             | 6 6              | 8 G 4            | • 2-3                       |

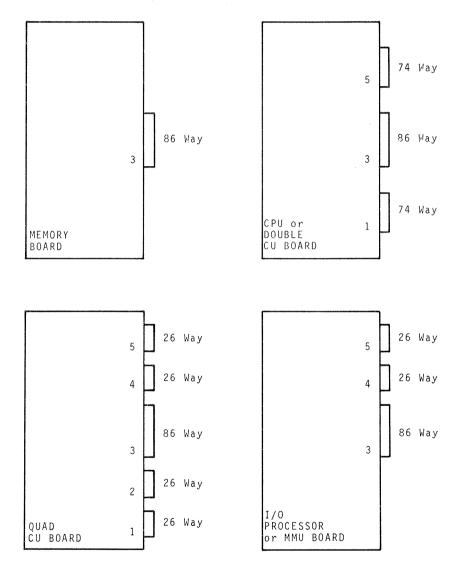

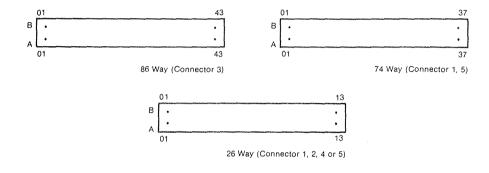

| Connector Details                    | ତି ଓ ଖ            | ê ê              | 0 0 V            | • 2-5                       |

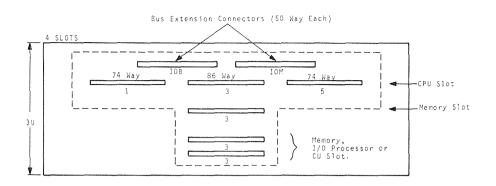

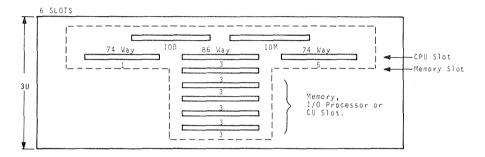

| Mounting Boxes Configuration         | 0 0 U             | ¢ 6              | • •              | • 2-6                       |

| Connectors IOM and IOB               | 8 6 0             | ë e              |                  | . 2-6                       |

| Method of Connection                 | e e ¢             | 8 C              | • •              | <b>.</b> 2 <del></del> 8    |

| Chapter 2 Bus - Programmed and $I/0$ | Process           | or Chanr         | nel .            | . 2-11                      |

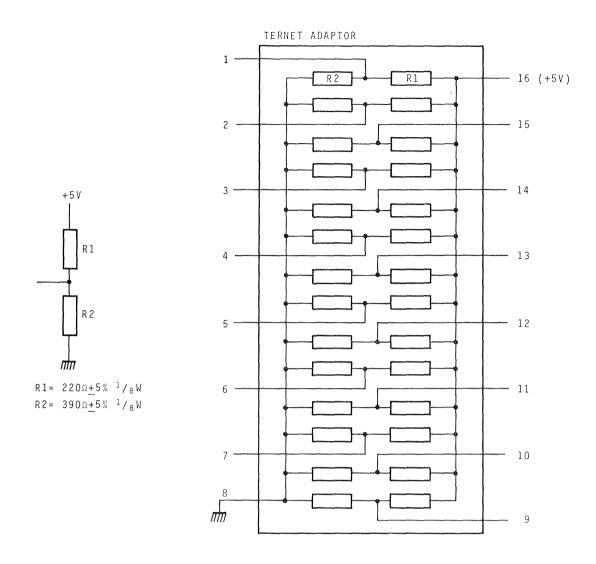

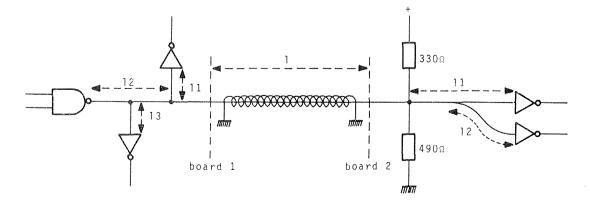

| Transmission Medium                  | 0 0 e             | • •              | • •              | . 2-11                      |

| Termination Resistors                | e e e             | 0 Q              | 9 6 G            | . 2-11                      |

| Connection Details                   | \$ <del>6</del> 0 | 6 O              | • • •            | . 2-12                      |

| Backpanel Addresses                  | 0 0 0             | • •              | • • •            | . 2-12                      |

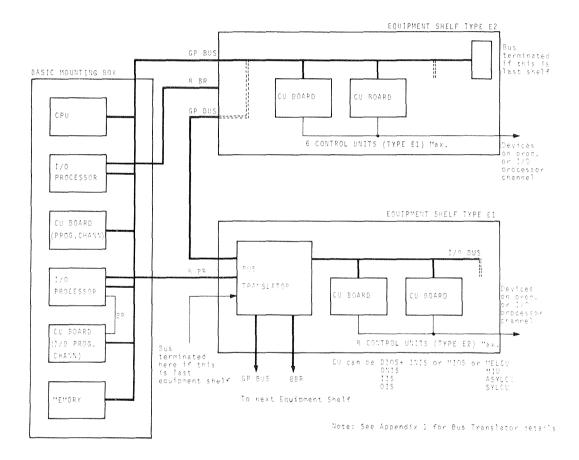

| GP Bus - Extension Connections       |                   | Ф В              | • • •            | . 2-14                      |

| Bus Translator Board Connections     | • • •             | • •              | 6 6 G            | . 2-16                      |

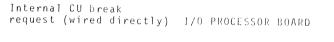

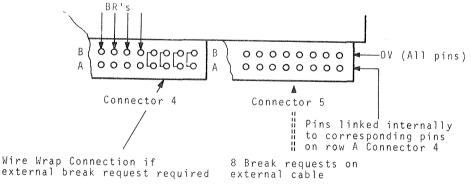

| Break Request Connections on $I/0$   | Process           | or .             |                  | . 2-19                      |

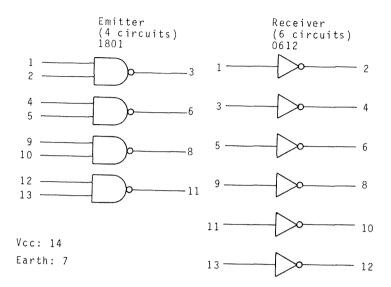

| GP Bus Interface Circuits            | 5 0 B             | e ș              | e 5 .            | <b>2</b> 20                 |

| Receiver 0612                        | 5 G 3             | • •              | • • •            | . 2- 20                     |

| Emitter 1801                         | 8 6 6             | <b>c</b> 6       | <del>6</del> 6 9 | . 2_20                      |

| Equipment Shelf Division Rules .     | 8 6 6             | 6 C              |                  | . 2. 21                     |

| Division Rules                       | 6 0 6             | ŭ ŭ              | 5 C I            | . 2-22                      |

| Break Request Connections            | 0 0 C             |                  |                  | • 2 <del>-</del> 23         |

|                                      |                   |                  |                  |                             |

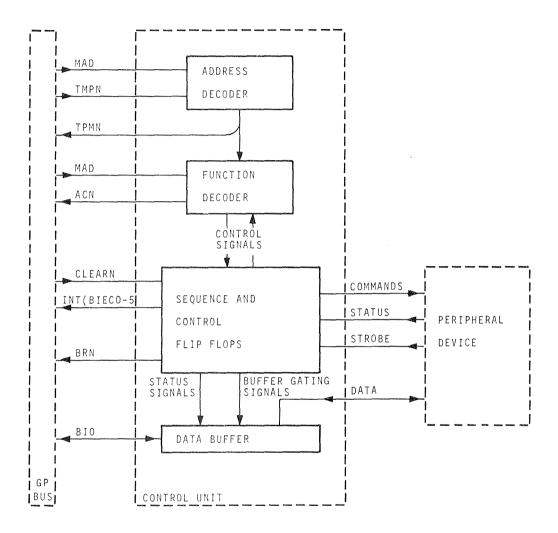

| Chapter 3 control Units              | * * *             | e e              |                  | • 2 <del>-</del> 25         |

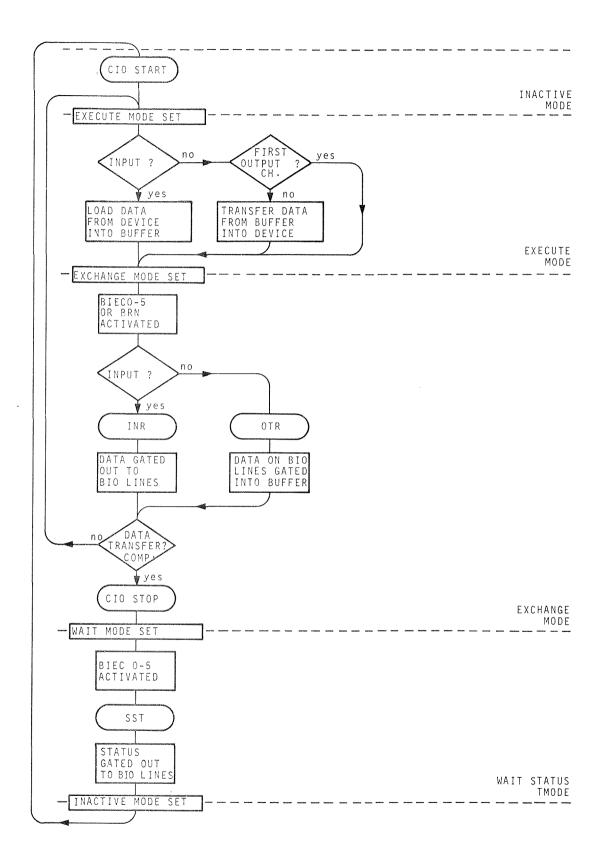

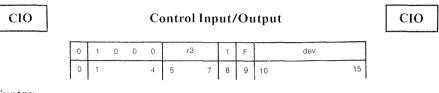

| CPU Commands                         | 8 Q Q             | 6 6              |                  | . 2-25                      |

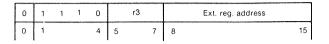

| Address                              | 0 0 0             | • •              |                  | . 2-26                      |

| Function Codes                       | 6 0 0             | ¢ 0              |                  | • 2-26                      |

| 50 <b>**</b>                         | 0 6 6             | e e              |                  | • 2- 26                     |

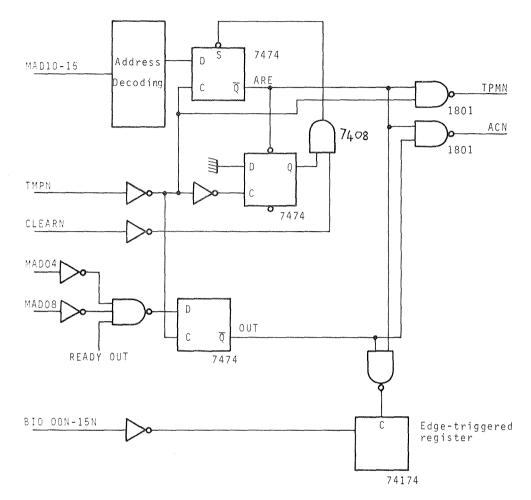

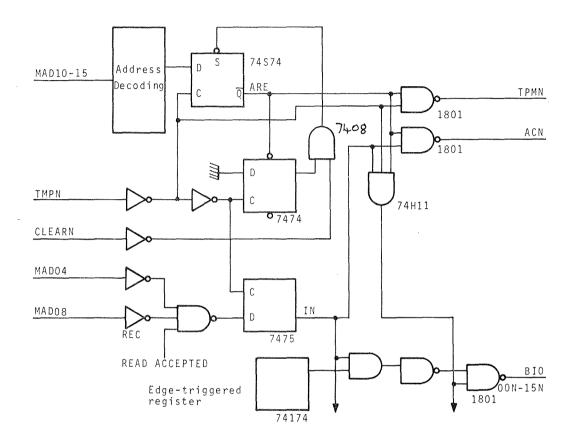

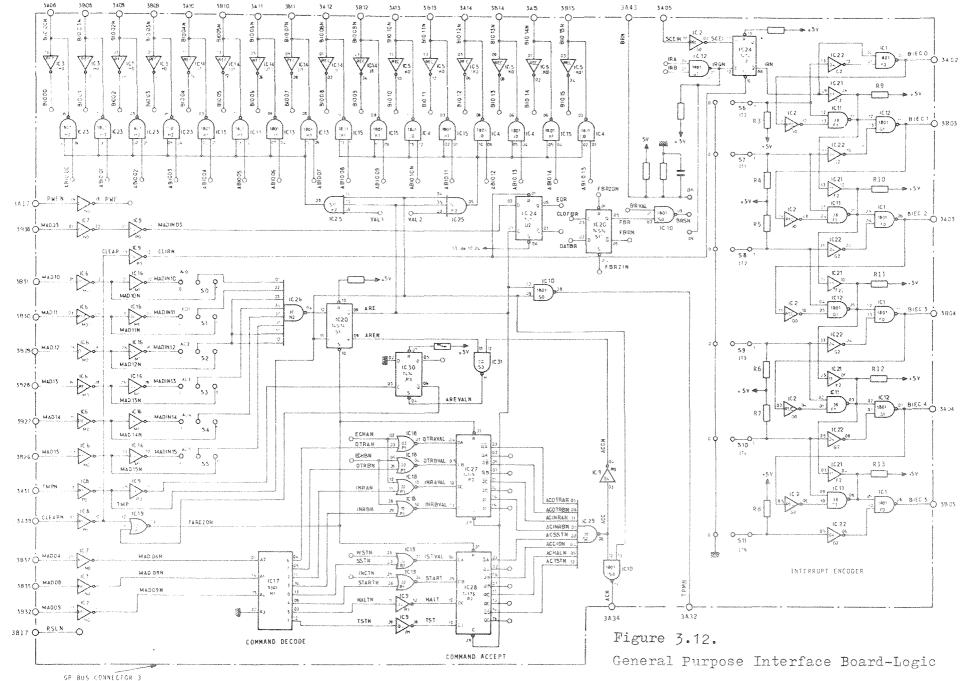

| Typical Control Unit - Logic Circu.  | its               | ÷ •              |                  | • 2 <del>-</del> 28         |

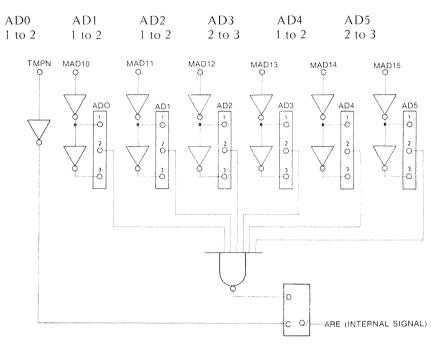

| Address Decoding                     | 0 C 6             | ¢ e              | • • •            | <b>.</b> 2 <b>-</b> 30      |

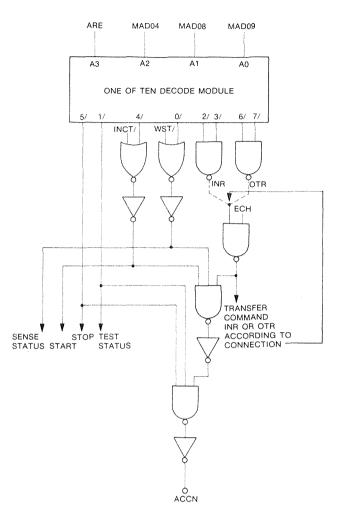

| Function Decoding                    |                   | 6 0              |                  | . 2-30                      |

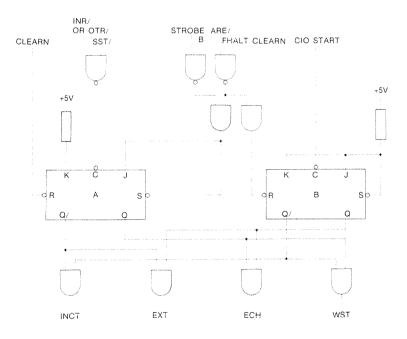

| Sequencing                           | Q Q Q             | 8 Q              | • • •            | • 2 <del>-</del> <u>3</u> 0 |

| Control Flip-Flops                   | 6 8 0             | e e              |                  | <b>2</b> 33                 |

•

|                                                                 |   | Page                |

|-----------------------------------------------------------------|---|---------------------|

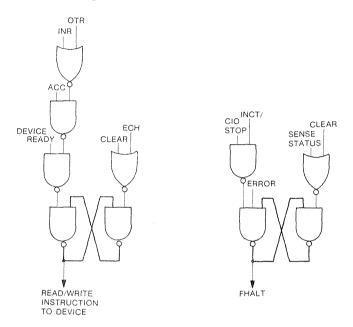

| Loading the CU Register                                         | • | 2-33                |

| Reading from CU Register                                        |   | 2- 34               |

| Programmed Channel or I/O Processor Selection                   |   | 2-35                |

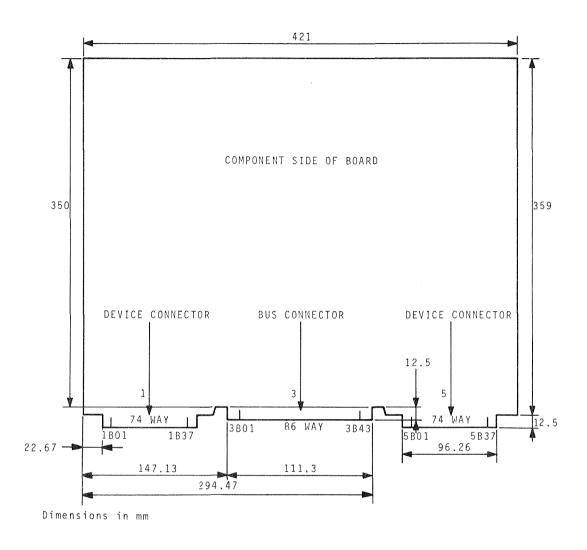

| Circuit Boards                                                  |   | 2-36                |

| Physical Details                                                |   | 2-36                |

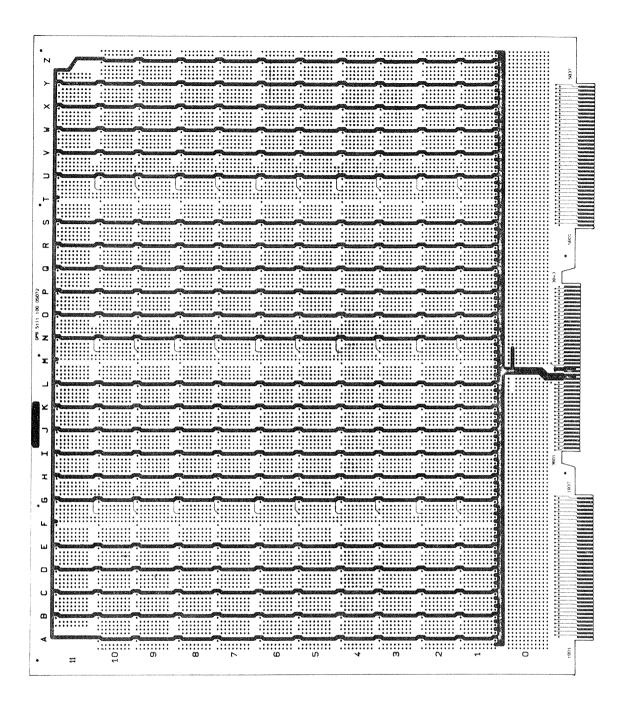

| General Purpose Wiring Board                                    |   | 2- 36               |

| Wiring Board Rules                                              |   | 2-36                |

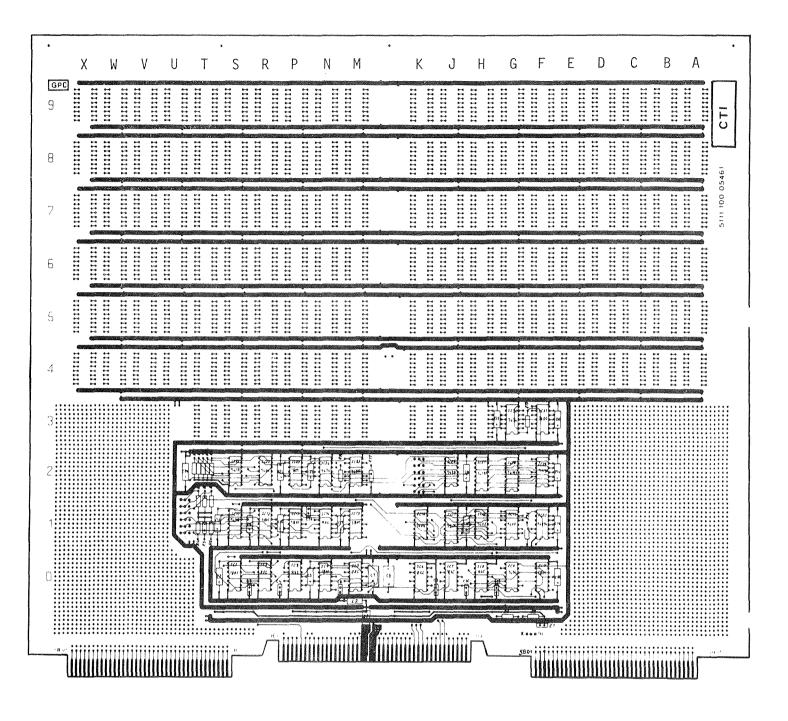

| General Purpose Interface Board for Type 1 Control U            |   | 2-39                |

| General Purpose Interface Board - Circuit Details .             |   | 2-39                |

| -                                                               |   |                     |

| Chapter 4 Wiring Board Rules                                    |   | 2-43                |

| Rules for Signals Remaining within a Board                      |   | 2-43                |

| Circuits with open Collector or a 3 State Output .              |   | 244                 |

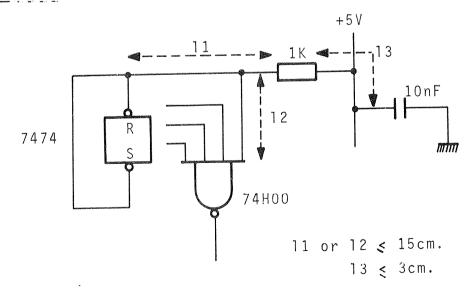

| Clock Circuits                                                  |   | 2-45                |

| Monostable Delay Circuit                                        |   | 2-45                |

|                                                                 |   | 2 <b>-</b> 45       |

| Unused Inputs                                                   |   | 2 <b>-</b> 46       |

| Bus Interface Signals - Wiring Board Layout Rules               |   | 2-47                |

| Layout Rules - Double Face Board                                |   | 2- 47               |

| Layout Rules - Multilayer Circuit                               |   | 2 <b>-</b> . 49     |

| Other Signals - Wiring Board Layout Rules                       | • | 2- 49               |

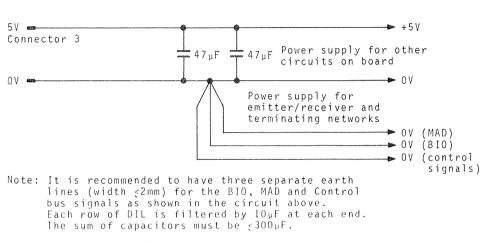

| Integrated Circuits Power Supply and Power Supply<br>Decoupling | _ | 2 <b>-</b> 50       |

| Bus Interface ICs                                               | • | 2 <b>-</b> 50       |

| Power Supply and Decoupling of other Circuits                   | e | 2 <b>-</b> 50       |

| Power Supply Distribution on Logic Boards                       |   | 2- 51<br>2- 51      |

| Integrated Circuit Equivalence Table                            |   | 2- <i>J</i> · 2- 51 |

|                                                                 |   | 2 <b>-</b> 51       |

| Back Panel (Motherboard)                                        |   |                     |

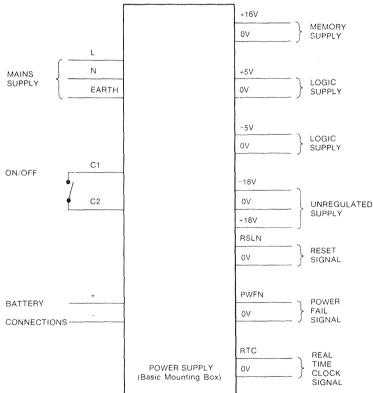

| Chapter 5 CPU Power Supply Interface                            |   | 2- 55               |

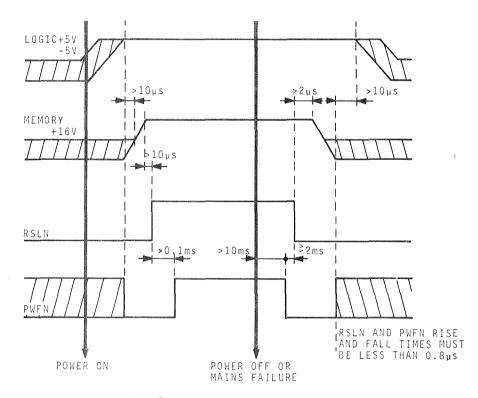

| Logic Signal and d.c. Supply Sequencing                         | • | 2 <b>-</b> 57       |

| Logic Signals                                                   | • | 2- 57               |

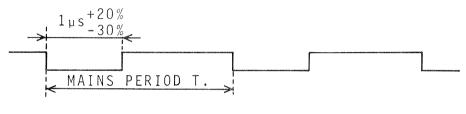

| Real Time Clock                                                 | • | 2- 58               |

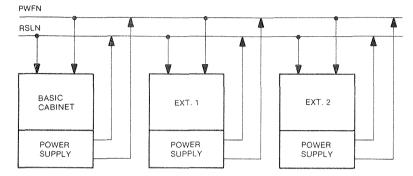

| Power Control when using Equipment Shelves                      | • | 2 <b>-</b> 59       |

| Chapter 6 DIOS                                                  | • | 2-61                |

| Basic DIOS Connections                                          |   | 2 <b>-</b> 61       |

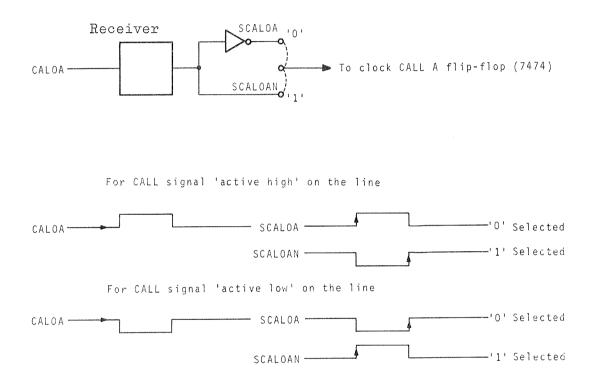

| CALL Signals                                                    |   | 2- 62               |

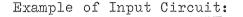

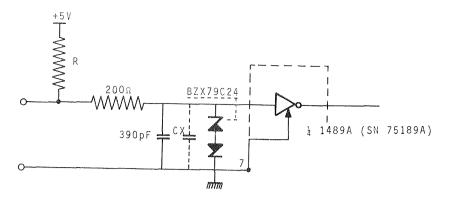

| Example of Input Circuit                                        |   | 2- 62               |

|                                                                 |   |                     |

|                                                     |      | Page                                    |

|-----------------------------------------------------|------|-----------------------------------------|

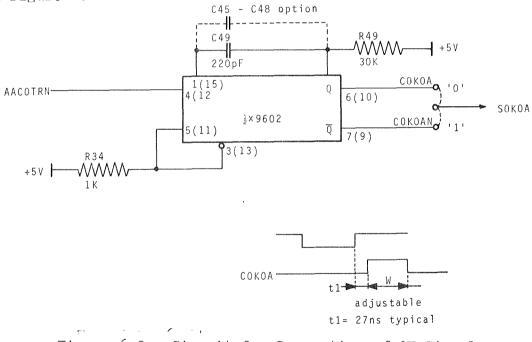

| OK Signals                                          |      | · 2- 63                                 |

| Interrupt Level Selection                           | •    | • 2- 64                                 |

| Address Recognition                                 | •    | • 2- 64                                 |

| Data Words Interface                                | •    | • 2 • • • • • • • • • • • • • • • • • • |

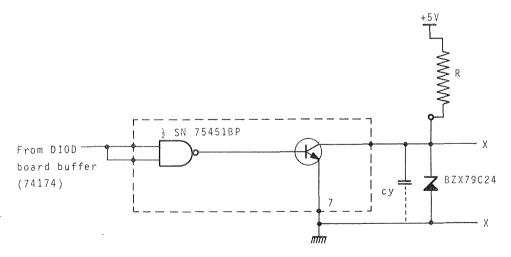

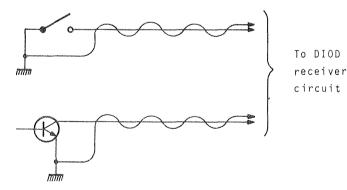

| Special Output Circuit                              | •    | • 2- 65                                 |

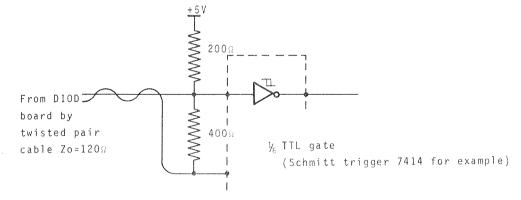

| Input Data Circuit                                  | •    | · 2-:65                                 |

| Pin Connections to DIOD Boards                      | •    | • 2- 67                                 |

| PART 3 INPUT/OUTPUT PROGRAMMING                     | ð    | • 3-1                                   |

|                                                     |      | 7 7                                     |

| Chapter 1 Introduction                              | ۵    | • 3= 3                                  |

| Peripheral Devices                                  | 8    | • 3- 4                                  |

| Basic Instruction Sequence                          | ٥    | • 3- 4                                  |

| Chapter 2 Input/Output Instructions                 | 6    | • 3-7                                   |

| CIO - Control Input/Output                          | a    | • 3 7                                   |

| TST - Test Status                                   | ٠    | • 3- 8                                  |

| OTR - Output from Register                          | ů.   | • 3- 9                                  |

| INR - Input to Register                             | ø    | . 3- 10                                 |

| SST - Send Status ,                                 | •    | • 3- 11                                 |

| WER - Write External Register                       |      | • 3 <del>-</del> 12                     |

| RER - Read External Register                        | 0    | . 3- 13                                 |

| Chapter 3 Modes of Data Transfer                    | ø    | • 3- 15                                 |

| Initiation of a Data Exchange                       | ٥    | • 3- 15                                 |

| Data Transfer in Wait Mode (Programmed Channel) .   | ٠    | • 3- 15                                 |

| Data Transfer in Interrupt Mode (Programmed Channel | ) 。  | • 3-19                                  |

| Data Transfer in Wait and Interrupt Mode (I/O Proce | ssor |                                         |

| Channel .                                           | ē    | • 3- 19                                 |

| Special Device Handling                             | 6    | • 3- 19                                 |

| Control Unit/Device Addressing                      | 8    | • 3- 23                                 |

| Chapter 4 Coding of Input/Output Drivers            | ۰    | • 3- 27                                 |

| Input/Output System                                 | •    | • 3- 27                                 |

| M:IORM                                              | ű    | • 3 28                                  |

| ENDIO · · · · · · · · · · · · · · · · · · ·         | 6    | • 3- 29                                 |

| COMIO · · · · · · · · · · · · · · · · · · ·         | ٠    | • <u>3- 3</u> 0                         |

| M:RETR                                              | •    | • 3- 32                                 |

| Chapter 5 Program Examples                          | ¢    | • <b>3-</b> 35                          |

| Example of an I/O Program in Interrupt Mode         |      | • 3 <del>-</del> 35                     |

| Example of a Program to read 20 characters via      | -    |                                         |

| I/O Processor                                       |      | • 3- 37                                 |

|                                                     |      |                                         |

•

SECTION 1 INTERFACING

PART 1

| 1.1 | General Structure of CPU's                      | • | • | 1-4           |

|-----|-------------------------------------------------|---|---|---------------|

| 1.2 | Block Diagram of P852M Data Handling Unit       | • | ٠ | 1-5           |

| 1.3 | Block Diagram of Data Handling Unit P856M/P857M | • | • | 1-9           |

| 1.4 | System Structure - Block Schematic              | • | • | 1-15          |

| 3.1 | Instruction Flow P852M                          | • | 8 | 1-25          |

| 3.2 | Instruction Flow P856M/P857M                    | • | • | 1-26          |

| 3.3 | Instruction Format                              | • | • | 1-27          |

| 3•4 | Timing-Writing in Memory (or External Register) | • | • | 1-31          |

| 3.5 | Timing-Read Memory (or External Register)       | • | • | 1-33          |

| 3.6 | Timing for an OTR Exchange                      | • | • | 1 <b>-</b> 36 |

| 3.7 | Timing for a CIO Exchange                       | • | • | 1-37          |

| 3.8 | Timing for INR, SST and TST Exchanges           | • | • | 1-40          |

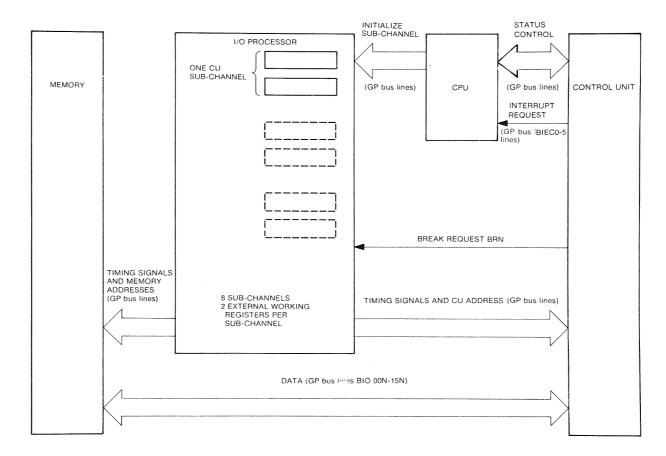

| 4.1 | I/O Processor Channel                           | • | • | 1- 44         |

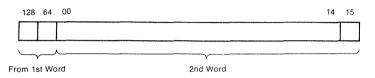

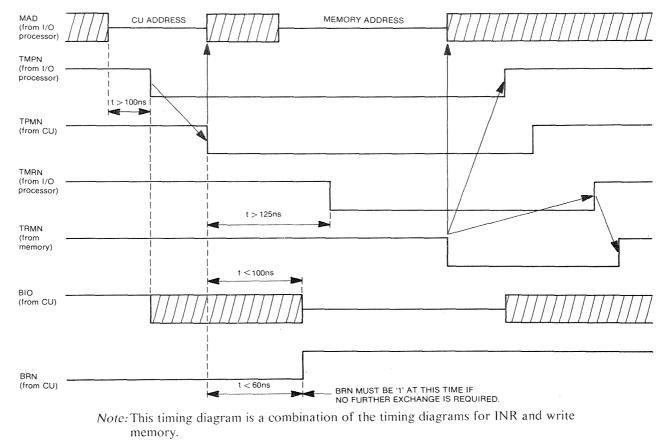

| 4.2 | Memory to CU Exchange-Timing Diagram            | ٠ | • | <b>1-</b> 48  |

| 4.3 | CU to Memory Exchange-Timing Diagram • • •      | • | • | <b>1-</b> 49  |

| 5.1 | Bus Control Priority Structure                  | • | • | <b>1-</b> 54  |

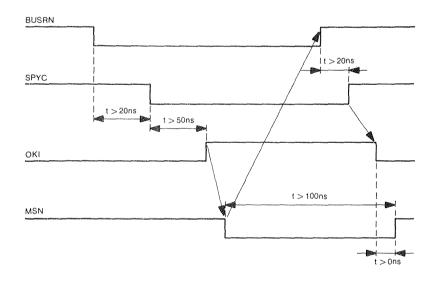

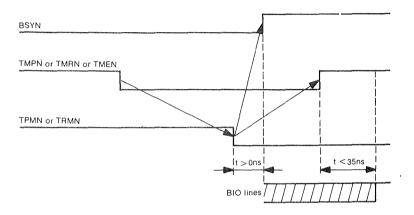

| 5.2 | Bus Request Timing                              | • | • | 1- 55         |

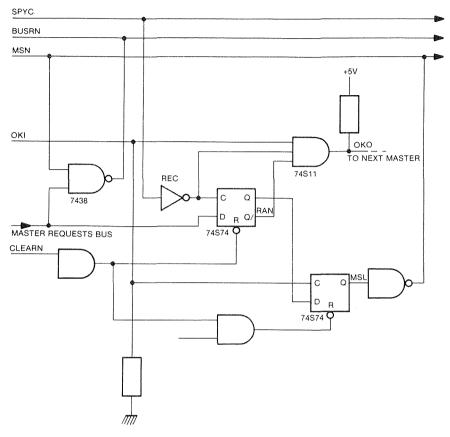

| 5.3 | Typical Logic Assembly                          | • | • | 1 <b>-</b> 56 |

| 5•4 | Priority Chain Timing                           | • | ٠ | 1- 57         |

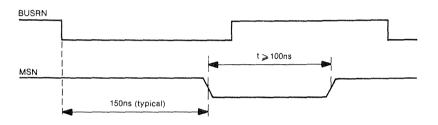

| 5.5 | Priority Chain Performance                      | • | • | <b>1-</b> 58  |

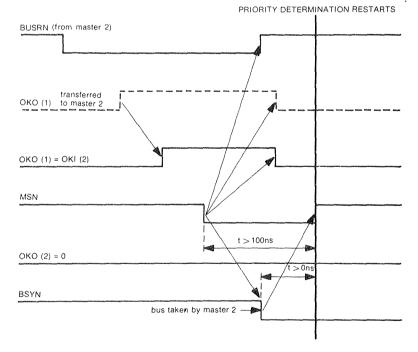

| 5.6 | Exchange Timing                                 | • | • | 1- 59         |

| 5•7 | Exchange Chaining-Master 1-CU, Master 2-RAM .   | ٠ | • | 1- 60         |

| 6.1 | Interrupt System                                | • | • | 1- 62         |

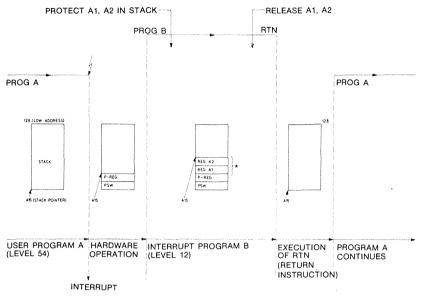

| 6.2 | Interrupt and Stacking System                   | • | • | 1 <b>-</b> 64 |

| 6.3 | Interrupt System Installation                   | • |   | <b>1-</b> 65  |

| 6.4 | Simplified Interrupt Encoding                   | • | • | 1- 66         |

| 6.5 | Signal SCEIN Timing                             | • | • | 1 <b>-</b> 67 |

| 7.1 | DIOD Interfacing Signals                        | • | 0 | 1- 70         |

| 7.2 |                                                 |   | • | 1-72          |

| 7.3 | GP Bus- Timing Diagrams                         | • | • | 1-74          |

| 7•4 | Timings for Control Lines                       | • | • | 1-76          |

|     |                                                 |   |   |               |

Y

PART 2

| 1.1  | Interface Connections                                                            | ٠ | 2-4           |

|------|----------------------------------------------------------------------------------|---|---------------|

| 1.2  | Printed Wiring Board-Connecter Layout                                            | • | 2-5           |

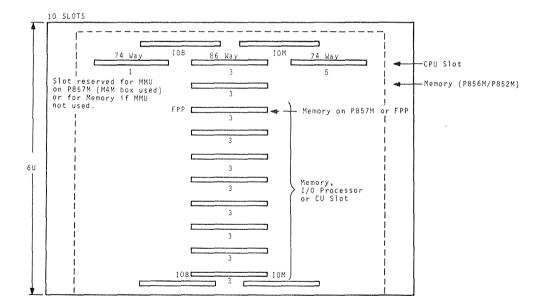

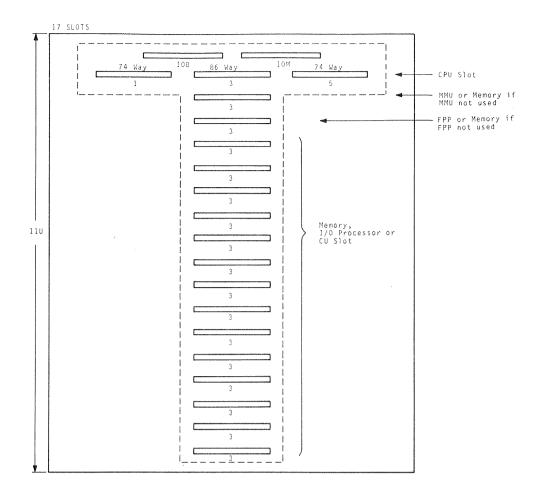

| 1.3  | Layout of Type M1 Mounting Box Slots<br>(P852M/P856M-100 Series)                 | • | 2-7           |

| 1.4  | Layout of Type M2 Mounting Box Slots<br>(P852M-200 Series)                       | ø | 2-7           |

| 1.5  | Layout of Type M4 (and M4M) Mounting Box Slots<br>(P852M/P856M/P857M-400 Series) | a | 2 <b>-</b> 7  |

| 1.6  | Layout of Type M5 Mounting Box Slots<br>(P857M-500 Series)                       | • | 2-8           |

| 1.7  | Break Request on I/O Processor Board $\ \cdot \ \cdot \ \cdot$                   |   | 2-9           |

| 2.1  | Terminator Bridge Adaption Networks                                              | • | 2-12          |

| 2.2  | Emitter 1801 and Receiver 0612 Pin Layout • • •                                  | ٠ | 2-21          |

| 3.1  | Control Unit Mode Sequences                                                      |   | 2-27          |

| 3.2  | Block Diagram of Typical Control Unit                                            |   | ŗ             |

|      | (P852M, P856M or P857M)                                                          | • | 2- 29         |

| 3.3  | Address Decode Logic                                                             | 4 | 2 <b>-</b> 30 |

| 3.4  | Function Decode Logic                                                            | • | 2-31          |

| 3.5  | Sequencing Logic                                                                 | ٠ | 2- 32         |

| 3.6  | Control Flip-Flops                                                               | • | 2- 33         |

| 3.7  | Loading the CU Data Register                                                     | • | 2-34          |

| 3.8  | Reading the CU Data Register                                                     | • | 2-,35         |

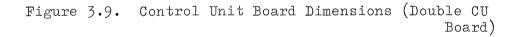

| 3.9  | Control Unit Board Dimensions (Double CU Board) .                                |   | 2-37          |

| 3.10 | General Purpose Wiring Board                                                     | • | 2- 38         |

| 3.11 | General Purpose Interface Board (P852M/P856M/P857M)                              |   | 2- 40         |

| 3.12 | General Purpose Interface Board-Logic                                            | • | 2-41          |

| 4.1  | Power Supply Filter Circuit                                                      | 0 | 2- 51         |

| 5.1  | CPU Power Supply                                                                 | 6 | 2- 55         |

| 5.2  | CPU Power Supply Interface Timing                                                | • | 2- 57         |

| 5.3  | Real Time Clock Signal                                                           | • | 2- 58         |

| 5.4  | System Using External Power Supplies                                             | • | 2- 59         |

| 6.1  | CALL Signal Input Circuit                                                        | • | 2- 62         |

| 6.2  | Circuit for Generation of OK Signal                                              |   |               |

| 6.3  | Output Driver Circuit                                                            | • | 2- 65         |

| 6.4  | Input Receiver Circuit                                                           |   |               |

|      |                                                                                  |   |               |

`

`

# PART 3

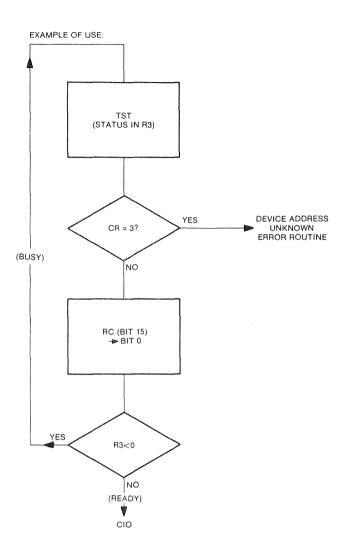

| 3.1 | Data Exchange | Initiation-with TST • • • • •          | 3-16 |

|-----|---------------|----------------------------------------|------|

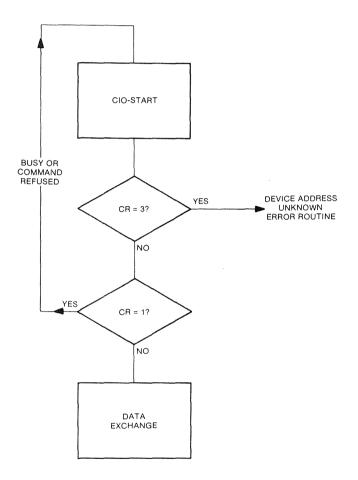

| 3.2 | Data Exchange | Initiation-without TST                 | 3-17 |

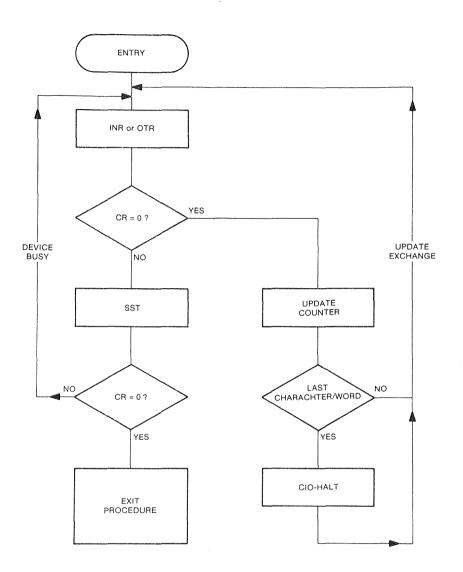

| 3.3 | Data Transfer | in Wait Mode (Programmed Channel)      | 3-18 |

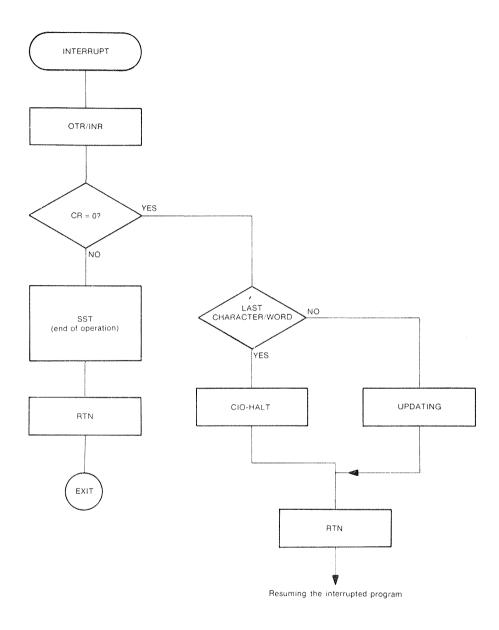

| 3.4 | Data Transfer | in Interrupt Mode (Programmed Channel) | 3-20 |

| 3.5 | Data Transfer | in Wait Mode (I/O Processor)           | 3-21 |

| 3.6 | Data Transfer | in Interrupt Mode (I/O Processor)      | 3-21 |

•

SECTION 1 INTERFACING

PART 1

|   | sonia sinta cana dinat | una della                                                     |                |

|---|------------------------|---------------------------------------------------------------|----------------|

|   | 3.1                    | Write in Memory CHA and MAD 15 bits                           | 1-30           |

|   | 3.2                    | Read Memory CHA and MAD 15 bits                               | 1-32           |

|   | 7.1                    | Command Instructions                                          | 1-73           |

|   | PART                   | 2                                                             |                |

|   | 2.1                    | Backpanel Addresses-Connector 3                               | 2-13           |

|   | 2.2                    | Connector IOM Connections • • • • • • • • • •                 | 2 <b>-</b> 14  |

|   | 2.3                    | Connector IOB Connections                                     | 2-15           |

|   | 2.4                    | I/O Bus Connections to Connector 1 $\ldots$ $\ldots$ $\ldots$ | 2-16           |

|   | 2.5                    | I/O Bus Connections to Connector 2                            | 2-17           |

|   | 2.6                    | Break Request Connections to Connector 7 • • • •              | 2 <b>_</b> 18  |

|   | 2.7                    | Break Request Connections to Connector 4 and 5 $$ .           | 2-19           |

|   | 4.1                    | Maximum Emitter Lengths                                       | 2 <b>-</b> .43 |

|   | 4.2                    | Integrated Circuit Substitutions                              | 2 <b>-</b> 52  |

|   | 5.1                    | Output Supply Characteristics                                 | 2 <b>-</b> 56  |

|   | 5.2                    | Logic Signals Characteristics                                 | 2 <b>-</b> 56  |

|   | 6.1                    | Pin Connections for DIOD1 and DIOD2 Boards                    | 2-68           |

|   | 6.2                    | Additional Pin Connections for DIOD2 Board (P837-002)         | 2-69           |

| - | PART                   | 3                                                             |                |

|   | 1.1                    | Connection of Peripheral Devices                              | 3-3            |

| [ • ] | connection of Peripheral Devices | • |   |   | • | • | • | ٠ | シーク           |

|-------|----------------------------------|---|---|---|---|---|---|---|---------------|

| 3.1   | Cassette Tape Operation          | Ð | ٥ | e | ¢ | ٠ | • | ٠ | 322           |

| 3.2   | Moving Head Disc Operation       | • | • | • | • | • | • | • | 3 <b>-</b> 23 |

| 3.3   | Example of CU/Device Addresses   |   | ٠ |   | ٠ |   | ٠ | e | 3-24          |

This manual is divided into the sections and parts summarized below, followed by an Appendix containing reference information.

#### SECTION 1 INTERFACING

# Part 1 Input/Output Organization

Describes in general terms the theory of operation and the structure of the computers and the integration of the input and output channels into the central processing functions. Examples of data exchanges, including timing diagrams, are given.

# Part 2 Interface Circuits and Hardware

Provides technical details regarding the locations and signal connections to connectors, interface circuit characteristics, signal levels and input/output loads and control unit design information.

### Part 3 Input/Output Programming

Contains the necessary information for the user to produce I/0 drivers other than those already existing for standard equipment.

SECTION 2 INSTALLATION

# Part 1 Site Considerations

Surveys various aspects which may require consideration when planning a site for a large configuration but which are not critical for the mini-computers themselves. Also provided in this part is information dealing with electrical supplies and interconnecting cables.

# Part 2 Central Processors and Integral Equipment

Describes the various types of central processor and also the equipment which is either located within the actual processor main-frame or constitutes an extension of it. As well as physical details and environmental requirements information is also given concerning equipment interdependent relationship, d.c. requirements and sources, control interconnections etc., to aid in the determination and installation of a suitable system arrangment. To allow for the possibility of future reinstallation at another site one chapter in this part gives details for adapting the various d.c. power supply units to operate from different main voltages.

# Part 3 Peripherals

Provides planning and installation data for each input and output device capable of being connected to the processing equipment described in Part 2. The data includes physical details, environmental and electrical power requirements and the standard lengths of the signal cables supplied with the equipment. The method used to convert each device to operate from different mains voltages is described briefly; full particulars can be obtained from individual supplier manuals.

# Part 4 Cabinetry

Gives details of the basic and extension racks, panels, mounting fixtures etc., which hold the equipment defined in Parts 2 and 3. The method of construction and the configuration rules governing the arrangement of the equipment in the racks are also described.

# Part 5 Installation Procedure

Is a general guide which outlines the unpacking and installation procedures for the equipment and the steps required to prepare the system for commissioning.

#### Appendices

Contains a list of useful reference manuals, some of which are referred to in the text and an example of a typical control unit logic circuit. Information is also given on the method used to translate signals from an I/O bus into GP bus signals when using, small format, control unit boards.

1-2

The P852M/P856M and P857M are advanced, general purpose, word oriented minicomputers which employ an asynchronous, general purpose bus to transfer information between the various elements connected in the systems. A powerful and flexible set of instructions are provided - including facilities for bit and character handling, long and short constant handling, stack handling, and FORTRAN facilities - coupled with a complete range of peripherals which enable the computers to be used in industrial, scientific, or general data handling applications; whether operating in real time or not.

Uncomplicated device control unit busing, straightforward device addressing, and unrestricted interfacing make the computers easy to integrate into a user's system - a prime consideration for the system engineer the programmer and, of course, the purchaser. The design of the CPU, employing microprogram control using a read-only memory, is easy to understand thus benefitting both the system and the service engineer, and the general purpose bus, which is used for both programmed data transfers and for block transfers is not subject to any critical timing or addressing restrictions - an advantage to the system engineer whether using the many available standard control units or designing control units to meet his own system requirements.

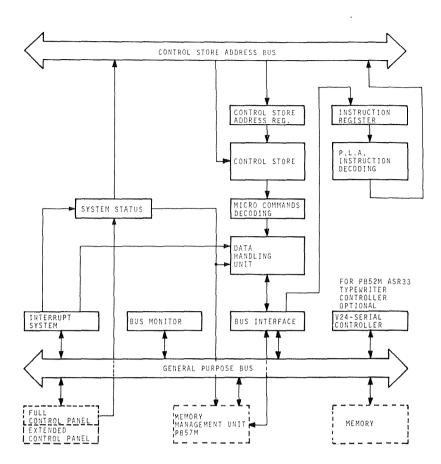

The functional block diagram given in Figure 1.1 shows the main units which form the hardware of the P852M, P856M,or P857M CPU structure. As the data handling unit of the P852M and the P856M/P857M differ in certain respects they are described, for convenience, under separate headings.

Figure 1.1. General Structure of P856M/P857M CPU's

#### DATA HANDLING UNIT

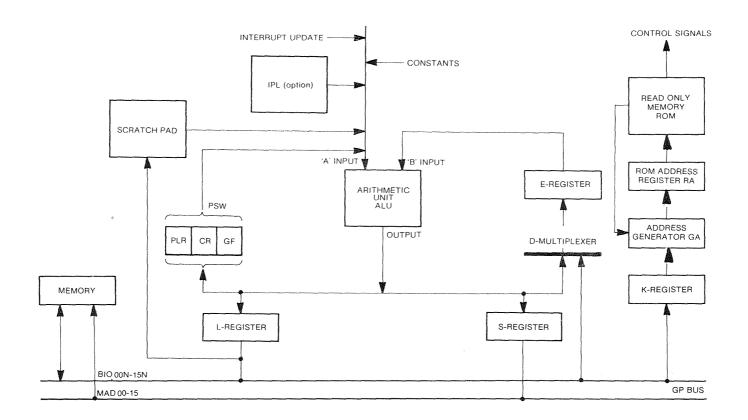

The relationship of the General Purpose Bus to the data handling unit components and the data paths through the unit are shown in Figure 1.2.

Data which is input from the General Purpose Bus(hereafter referred to as the GP bus) is routed, via multiplexer D, to shift register E which provides an output to input 'B' of the arithmetic and logic unit(ALU). Input 'A' of the ALU is provided from any one of four sources as follows:

Figure 1.2. Block Diagram of P852M Data Handling Unit

- 1. The contents of any of the scratch pad registers.

- 2. The contents of the Initial Program Loader (IPL) An optional extra.

- 3. A program status word (PSW) a word holding information concerning the current status of the running program.

- 4. Any constants which may be required in the execution of the current instruction.

The output from ALU may be transmitted to:

- 1. Register L and from there to either the scratch pad or the GP bus.

- 2. Memory address register S.

- 3. The E register, via multiplexer D, and from there to the ALU for further processing.

- 4. The PSW register for updating the PSW.

The instruction to be carried out is derived from the GP bus by the K register and is output to address generator GA. This generator produces the appropriate microprogram addresses and transmits them via ROM address register RA to the read-only memory ROM. The ROM then generates microinstructions to the CPU hardware units to control the execution of the instruction.

Priority level register PLR carries the priority level of the running program and condition register CR records the current program state of the CPU. The block defined on the diagram as GF contains six flip-flops and this block, together with the PLR and CR blocks, are all considered to be functionally part of the PSW whose states both influence and indicate the status of the CPU.

The hardware components shown in Figure 1.2 are:

| MEMORY UNIT            | A 16-bit word <b>1.2</b> usec core memory expandable from 4k up to 32k words. Connection of a MOS memory is possible. The core memory is available in modules of 4k, 8k, and 16k. The memory is addressed directly via the GP bus and receives or provides data also directly to the GP bus.                                                                                                                                                                                                                                                                                                                           |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCRATCH PAD            | A block of 16, 16-bit program accessible registers.<br>A0 is the program instruction counter (P register)<br>and A15 the stack pointer for the interrupt system.<br>The remainder are available as accumulators. The<br>registers are addressed by the instruction word<br>received in the K register or by the scratch pad<br>address keys on the control panel. Data from the<br>scratch pad is loaded into the ALU for processing<br>and is then output to the GP bus via the L register.<br>The scratch pad registers can accept data from<br>memory via the D multiplexer and E register, ALU,<br>and L register. |

| ARITHMETIC<br>UNIT ALU | A 16-bit parallel processing unit operating in true binary, two's complement. It performs arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

and logic operations on the data provided at input "A", from one of four sources and at input "B",

|                                                | can be output to register L, register S, to the E register via multiplexer D, or to the PSW register.                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMULTIPLEXER                                   | <ul> <li>A 16-bit multiplexer which can be operated as a 2 × 8-bit multiplexer. The inputs to the multiplexer are either from the GP bus or from the ALU output and it provides inputs to the E register as follows:</li> <li>1. Data read from the GP bus.</li> <li>2. Intermediate results from the ALU to be stored in E.</li> <li>3. A short constant from the ALU.</li> <li>4. The values in the PLR register during interrupt procedures.</li> </ul> |

| E REGISTER                                     | A 16-bit register used in shift operations. The register also acts as an input and output buffer for the ALU and as a buffer for signals read from the GP bus via the D multiplexer.                                                                                                                                                                                                                                                                       |

| K REGISTER                                     | Instruction register loaded from the GP bus lines<br>with the instruction to be executed. Output from the<br>register is to the ROM address generator GA and<br>is also used to address the scratch pad.                                                                                                                                                                                                                                                   |

| L REGISTER                                     | A 16-bit register used for temporary storage for results from the ALU which are to be passed to the scratch pad or to the GP bus.                                                                                                                                                                                                                                                                                                                          |

| S REGISTER                                     | A 16-bit register arranged as a synchronous down<br>counter. It performs 3 functions — acts as the<br>address register for the addresses of the memory,<br>external register, and control units; elicits from<br>scratch pad register A15 the current value of the<br>stack pointer; acts as a loop counter for the<br>microprograms.                                                                                                                      |

| PLR/CR/GF REGISTER                             | A 16-bit program status word register holding the priority level of the running program, the 2-bit condition register CR and 8 status bits.                                                                                                                                                                                                                                                                                                                |

| ROM ADDRESS<br>Generator ga<br>And register ra | A generator which derives the appropriate ROM addresses from the instructions of the running program, the current state of the CPU, and from the ROM output, and a register which provides the address of a single microprogram word to the ROM input.                                                                                                                                                                                                     |

| READ-ONLY<br>MEMORY (ROM)                      | Holds 512, fourty eight-bit words and Contains a series of micro-instructions which control the CPU data processing elements in order to carry out the execution of the instruction set.                                                                                                                                                                                                                                                                   |

from the E register. Data from the arithmetic unit

| INTERRUPT SYSTEM | A system which compares the highest priority level<br>interrupt received, either externally or internally,<br>with the priority level of the running program,<br>contained in the PLR register, and provides an<br>interrupt output signal, if interrupts are allowed<br>and if the received interrupt is of higher<br>system also provides an output to update the PLR<br>register with the priority level of the new interrupt.         | priority. |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1/O PROCESSOR    | A unit containing the logic to operate peripheral control units on the GP bus in multiplex mode. In this mode of operation blocks of data are transferred between a control unit and memory via the GP bus, each character or word transfer being initiated by a break request BR from the control unit. The transfers are controlled by the $I/0$ processor independently of the CPU and simultaneously with the running of the program. |           |

DATA HANDLING UNIT P856M/P857M

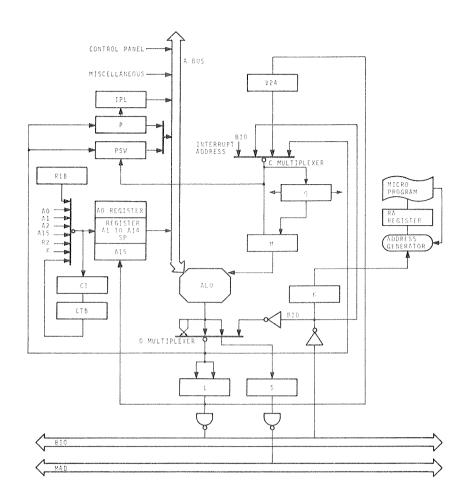

The data handling unit components for the P856M and P857M and the data paths through the unit are shown in Figure 1.3. Data which is input from the GP bus is routed to multiplexer C (via multiplexer D) and then to register M which provides an output to input B of the ALU, or to register L or S. Input A of the ALU is provided from the same sources previously described for the P852M.

The output from the ALU is switched via the D-multiplexer as follows:

1. As a direct or character swap output to the L-register, P-register, PSW register (GF bits) and C multiplexer. The L-register output is taken to the scratch pad and V24 serial controller and (if gated) to the GP bus. From the C-multiplexer the ALU output can be returned, via register M, to the B input of the ALU for further processing.  As an output to memory address register S the output of which (if gated) is taken to the address lines of the GP bus.

Figure 1.3. Block Diagram of Data Handling Unit P856M/P857M

The micro-instructions to control the CPU hardware are derived as previously described for the P852M data handling unit. The main differences for the hardware components of the P852M and P856M/P857M data handling units are given below. Note: A description is not given for a component which functions in a manner previously described for the P852M.

MEMORY UNIT A 16-bit word core memory (cycle time 1.2  $\mu$ s or 0.7  $\mu$ s for P856M and 0.7  $\mu$ s for P857M) expandable in 8K or 16K modules (1.2  $\mu$ s) or 16K modules (0.7  $\mu$ s) up to 32K for P856M and 128K for P857M. Connection of MOS, ROM and/or PROM memory is possible. SCRATCH PAD A block of 15, 16-bit program addressable registers A1 to A14 are available as accumulators and A15 functions as a stack pointer for the interrupt system; it may also be addressed from the instruction format. The registers are addressed by the instruction word received in the K register. A counter and counter buffer (CT and CTB) are used to address sequential scratch pad registers during multiple Load or Store instructions or to count repeat cycles for sequensor control.

D MULTIPLEXER A 16-bit selector or 2x8-bit multiplexer used as a control element in the arithmetic loop. The inputs to the multiplexer are from the ALU or from the GP bus and it provides outputs in 4 modes as follows:

> ALU output- direct(inverted output) -shift right-input to S register(true output) -character swap(inverted output) GP bus input(inverted output)

The inverted output is sent to the L register, PSW register, instruction counter P, and to the C multiplexer. The true output is sent to S register - this mode is used for shift right and multiplication operations.

C MULTIPLEXER A 4 input selector in the operand 'B' input data path of the ALU for two 16-bit sources which can be selected as long or short constants(D multiplexer output, BIO lines output)and two 8-bit sources (Interrupt address,V24 serializer output). The selected outputs are switched to the Q and M registers and the six least significant bits of the interrupt address are also sent to the PLR register(part of PSW register)during an interrupt routine. M REGISTER A 16-bit multiple input register. Used as

A TO-BIT Multiple input register. Used as a working register and buffer in the operand 'B' input data path to the ALU for inputs provided via the C multiplexer or from the Q shift register.

- P REGISTER A 16-bit synchronous register/up-down counter used to hold the address of the next instructions to be executed. The register is loaded(via the D multiplexer) with the 14-bit word address of the program; the register is also used as an internal counter during multiple word instructions.

- Q REGISTER A 16-bit left/right shift register. Used during double length instruction operations.

- IPL A 64-word Initial Program Loader bootstrap (ROM) of 256 four bit words(regrouped into 16-bit words when loaded into memory),which provides the system with the ability to automatically load and run an initial program loader or similar program from devices on either the programmed or I/O processor channels. The IPL is standard on the P857M and pptional on the P856M.

#### MEMORY MANAGEMENT UNIT (P857M)

A memory management unit (MMU), provided as standard with the P857M computer, gives the facility to access primary memory over 32Kw up to 128Kw (and practically unlimited space in secondary storage, such as high speed discs), permits dynamic program relocation, and offers a memory protection facility. Special instructions are provided for this unit.

Using the MMU gives the user a virtual memory system, with the ddvantage of working in a real time multiprogramming or multi, tasking environment. The system is transparent to the user, who does not need to know where in primary or backing store, his program is located. A user program may not exceed 32Kw.

In operation the MMU dynamically translates a normal 16-bit program address(logical address) into a 18-bit physical address (real address) which is used to address one of 64 pages, each of 2Kw, in primary memory(the pages do not need to be consecutive). When used in system mode the system uses the logical 16-bit address-no translation is performed-as it always resides within the first 32Kw of primary memory. In user mode however the logical addresses are always translated by the MMU into physical addresses; to address the pages in memory a segment table(16x16 bits)is built for each program called. The bits 0-3 of the logical address from the beginning of the page. The segment address locates a register in the segment table which then outputs a 6-bit physical page number and this, together with bits 4-15 from the logical address is used to produce the 18-bit physical address.

Memory protection is provided by a special interrupt 'Page Fault' which is given when an attempt is made to write into a protected page or when a missing or wrong page is tried to be accessed. The interrupt has priority over other internal or external interrupts.

EXTRA FACILITIES (P856M and P857M)

#### Memory Interleaving

Memory interleaving is possible, using 0.7 µs read/write core memory, which permits very fast execution of instructions. The access time comprises one read cycle after which the execution of the instruction starts immediately. To make full use of the capability the minimum memory size is 32Kw i.e. 2 modules of 16Kw each (one module will contain even addresses and the other the odd addresses; the CPU automatically applies interleaving (if the links have been made on the memory boards).

#### Micro-diagnostics

To aid in fault location a 100-word microdiagnostic program (contained in the micro-program ROM) is available which permits testing of the data paths, control unit-CPU dialogue, and memory. Automatic or step by step of the CPU-CU dialogue and the first 4K words(P856M) or 16K words(P857M) of memory is possible; the test program is made available by simply setting a key on the control panel to a position marked 'TEST'.

#### Extended Control Panel

A dual display control panel is included as standard on the P857M(optional on the P856M)which enables the entire memory to be addressed and also provides facilities for a quick and easy inspection of the memory contents- a valuable aid for software/system testing. A'stop on preset' facility is provided, for program debugging purposes.

#### INPUT/OUTPUT CHANNELS

Dialogue in the systems is in asynchronous conversational mode which is easily adaptable to the system elements involved. The exchanges which can take place and the channels used are summarized as follows:

Exchange CPU and Control Unit Control Unit and Memory CPU and External Memory Channel Used Programmed 1/O Processor

One of the most important system features is that they permit peripheral control units to make direct transfers with memory under control of an I/O processor which has an interface identical to that required for the programmed channel.

The choice of which channel to use depends on the type of device to be connected and the application for which it is to be used. Programmed channel, where the transfer is word or character oriented is used only for low speed applications such as the operator's typewriter or punched tape or card devices. When using the I/O processor, however, the programmed channel is also used to initially transfer the contents of two control words, which govern a block transfer, into the I/O processor and to activate the control unit to be used during the transfer. The execution of a program, when using the programmed channel, may be interrupted either by the generation of an internal interrupt signal or by an exchange request from a system element which is conveyed to the CPU on the interrupt request lines of the GP Bus.

The I/O processor provides for the control and automatic execution of direct transfers of variable-length blocks of data in either direction between control units and the block or blocks of central memory. The channels are used normally by high speed devices but can be used also by low speed devices. As many as 64 control units, operating on a priority basis, can be controlled via the channels. Requests for data transfers are made from control units using a system of break requests signal lines connected between the I/O processors and the control units. These signal lines are carried on separate cables which do not form part of the GP Bus.

A direct memory access facility can be used with the standard systems by designing a control unit which contains its own logic for obtaining access to memory and registers containing control words to govern the block transfer. A data transfer using this facility would then occur at memory speed.

# ź GENERAL PURPOSE BUS

All transfers of information between elements of the system take place via the lines of the GP Bus<sub>\*</sub>, The bus lines, which are described in more detail in chapter 2, can be subdivided into groups as follows:

| Data and Control            | Data    | (18 lines)CLEARN(16 lines)ALN(5 lines)CHA                        |

|-----------------------------|---------|------------------------------------------------------------------|

|                             | Others  | (1 control unit response, WR<br>4 internal signals, 1 clear)     |

| Master Selection            | 5 lines | SPVC, ORO, MSN, BSYN, BUSRN total                                |

| Interrupt Request<br>Others |         | (including 1 scanning line)<br>(power control and power failure) |

With such a bus, which is asynchronous and multiprocedural, peripherals have individual address and can be addressed directly, via the bus. In addition the dialogue over the bus is more efficient as, with each type of dialogue, a procedure is associated which is specifically suited to the function being carried out.

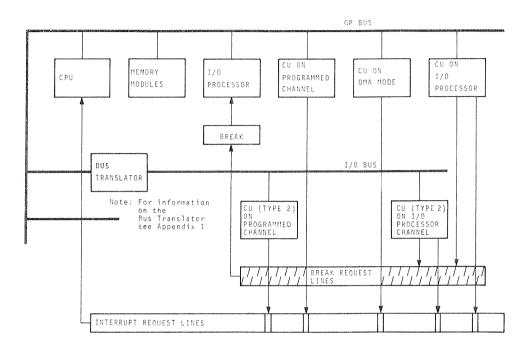

The system concept is illustrated in Figure 1.4 which shows how all data handling system components are connected. Some control units (defined as Type 1) are connected directly to the GP Bus and others (defined as Type 2) are connected to an I/O bus and, via a bus translator, to the GP Bus.

#### MASTER-SLAVE RELATIONSHIP

Communication between two devices on the GP bus employs a master-slave relationship and during any bus exchange operation one device, called the master, has control of the bus when communicating with another device, called the slave. For this relationship a system element which can receive control of the bus to address memory is defined as a master and a system element which has not the possibility to address memory is called a slave. I/O processors and DMA controllers (if used) are examples of masters. The memory, the registers, and the device control units are always slaves.

The master of an exchange may address a slave or another master (which then functions as a slave); a priority control system determines which master obtains control of the bus. In any exchange involving the CPU, however, the CPU is always master of the bus.

#### PRIORITY STRUCTURE

A number of masters may be connected in the system and a bus controller is provided to regulate the access of the masters to the bus in order of priority of their requests. The CPU has automatically direct access to the memory (via the bus) at the end of the execution of each instruction if no other device is requesting or using the bus.

#### EXTERNAL CONNECTION

All peripheral units and data input or output devices are connected to the GP bus by means of control units. These can be single boards located in slots in the basic mounting box, or in an equipment shelf, or may consist of several boards housed in an equipment shelf. For P852M computers the control unit for an ASR typewriter may be constructed on the CPU board or may be a separate control unit. For P856M and P857M computers a V24 serial control unit is provided as standard on the CPU board.

Addressing facilities for up to 256 external registers are provided on all computers.

#### **Standard Control Units**

Peripheral control units are available to suit many types of peripherals including I/O typewriters, punched tape readers and punches, line printers, punched card readers, magnetic disc and tape readers, and cassette tape units. The control units are either connected directly to the GP Bus or are connected to the GP Bus via bus translator boards.

For general purpose digital input and output of up to 16 bits per channel the digital input/output (DIOS) system of control units is available Using Dual Input Output boards (DIOD).

Figure 1.4. System Structure - Block Schematic

Analog or digital acquisition is handled by a modular input/output control(MIOS)system,which includes output units for driving display equipment, and an analogue/output (AIOS)system can be provided as an analogue data channel For further details refer to the MIOS manuals listed in the Appendix.

Data Communication in the systems is accomplished by the use of multiple line control units, both synchronous and asynchronous, at speeds up to 200,000 baud, and asynchronous line multiplexers at speeds up to 9600 baud. For further details refer to the P852M/P856M/P857M Data Communication Service Manual listed in the Appendix.

#### User Designed Control Units

To aid the user wishing to build his own control units for special applications there are two styles of general purpose board; one is already equipped with I/O control logic while the other is completely blank but has a hole pattern for accepting 226(14 or 16 pins) IC's and 15 MSI LSI packages with 24 or 40 pins as well as components or wire wrap pins.

#### **Control Unit Operation**

Each control unit has a unique address that is decoded from the lines of the GP bus which carry the address, thus any control unit can be addressed by software I/O instructions. Similarly the function lines of the GP bus are decoded to permit control of the associated peripheral device by software instructions. Recognizing its address the control unit decodes the function and then provides the necessary control signals or data synchronisation pulses to its peripheral.

#### **INTERRUPT SYSTEM**

When a control unit operating on programmed channel has been switched into service by a software I/O instruction it will give an interrupt request to the CPU when it is ready to send or receive data. The CPU may then service the interrupt request and interrupt the program according to the priority level assigned to the interrupt. Eight interrupt levels, 0 to 7, are included in the minimum configuration all of which arise within the basic mounting box; of these eight, four are interrupts generated inside the CPU. The interrupts may be increased to a maximum of 63 with the addition of levels 8 to 62 which may originate inside or outside the basic mounting box. In this case the interrupts are conveyed to the CPU on 6 separate lines of the GP Bus using a bused system which transmits a coded signal representing the interrupt level having the highest priority, which has been raised.

The state of all interrupt lines is sampled upon the completion of each one or sometimes two program instructions (fetch cycle) and compared with the priority level of the running program. If there is an interrupt request having a higher priority than that of the running program an interrupt routine is initiated by the interrupt, provided that the CPU is in the enable interrupt state. Return to the original program is made possible by storing the memory address at which it must restart.

The interrupt system makes use of automatic stack handling to service both internal and external interrupts. This means that, for each interrupt the contents of the P register (this is the address at which the program must restart) and a status word are stored in a part of the memory allocated for interrupt stacking. Access to the stack is made from scratch pad register 15 which always points to the next location in the stack. The stack pointer is automatically decremented each time program information is loaded into the stack and is incremented when information is removed from the stack to run a program. Automatic indication of stack overflow is given to warn the programmer that the stack is nearly full and unable to handle further interrupts.

#### **Internal Interrupts**

The following four interrupts are generated inside the CPU:

- Power Failure

- Program Interrupt

- Real Time Clock

- Control Panel

of these interrupts two are used in all configurations and these are:

| Program Interrupt | This occurs if the stack overflow condition arises or if a Link to Monitor instruction is executed. |

|-------------------|-----------------------------------------------------------------------------------------------------|

|                   |                                                                                                     |

**Control Panel** This is instigated by pressing the INT button.

The other two interrupts are generated by power failure or real time clock.

Internal interrupts within the CPU are handled in exactly the same manner as external interrupts except that, to be effective, the power failure interrupt must be assigned the highest priority level (lowest number) above all other internal and external interrupts.

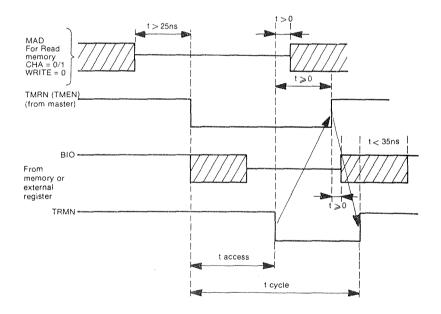

#### TIMING CONTROL SIGNALS

Exchanges between masters and slave units are controlled by timing signals (from master) and timing response signals (from slave). The timing signals are used to validate addresses and data and to control the overall timing of an exchange. Use of such an asynchronous timing system permits either standard or non-standard peripheral devices to be used without the need for special timing circuits.

Further details of the timing signals used are given in Chapters 3 and 4 of this Part where timing diagrams are provided for the various exchanges possible.

All transfers of information between elements of the P852M/P856M or P857M system take place via the GP bus, and the lines of the bus comprise the input and output signal and address lines necessary for the data transfer requirements of the system. The GP bus can be extended outside the basic mounting box to further equipment shelves by using 125 ohm, flexible, plug-in, trans-mission lines. The lines can be extended in convenient lengths between equipment shelves up to a total max-imum length of 14.5 metres. Line termination facilities are provided in the basic mounting box and, if required, in the equipment shelves .

Termination details of the GP bus lines are given in Part 2 of this Section of the manual together with the characteristics of the emitters and receivers required to interface with the GP bus lines.

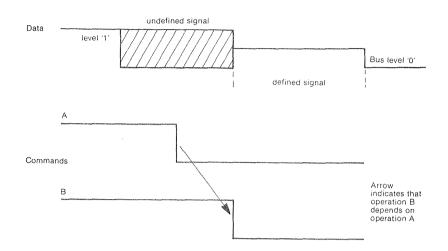

Two types of signal are used on the bus: command signals and data signals. Command signals are those which will cause an immediate action according to their change of state; these signals have no unknown state but are always either logic "1" or "0". Data signals carry the actual information exchanged amongst the system elements; these signals are permitted to adopt indeterminate values except when the information is actually being used in the processing.

The signals carried by the GP bus lines are described below. When a mnemonic ends in "N" it means, in the case of a data signal, that the signal transmitted on the GP bus is the complementary value of the true signal. In the case of the control signal the "N" means that the signal performs its function on being set to "0" (active low). Most of the GP bus lines are used both inside and outside the basic mounting box. Where this does not apply it is indicated in the signal description given below.

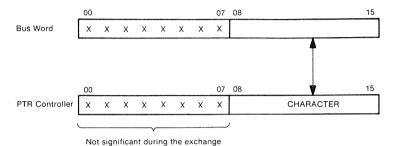

**GP Bus Signals** BI0 00N to BI0 15N

16 data lines which are used to carry data information between all system elements concerned with the transmission or reception of data signals.

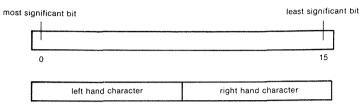

#### The bit location is as follows:

(only MAD03, 04,08-15 used externally also)

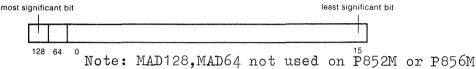

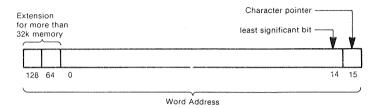

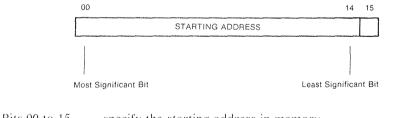

MAD128, 64 and 00 to 15 18 address lines which carry different information according to the type of exchange. The bit location is as follows:

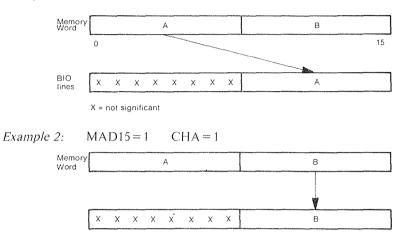

For a master-memory exchange the MAD lines carry the memory address and MAD15 is used as a character indicator. When set to 1 it indicates the right (least significant) character and when set to 0 the left (most significant) character.

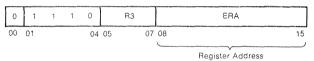

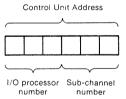

For a master-control unit exchange the lines MAD10-15 carry the address of the control unit and lines MAD 04, 08 and 09 the function to be performed. MAD03 indicates whether or not the exchange in progress is the last. The functions are as listed below:

| MAD04 = 0 | exchange to control unit |

|-----------|--------------------------|

| MAD04 = 1 | exchange to master       |

| MAD08 = 0 | data exchange (INR, OTR) |

| MAD08 = 1 | command or status        |

|           | exchange                 |

| MAD09     | special functions        |

| MAD03 = 0 | exchange not the last    |

| MAD03 = 1 | last exchange.           |

For a master-external register exchange the lines MAD08 to 15 carry the address of the external register. MAD04 is used to indicate whether it is a read or write operation as follows:

| MAD04 = | 0 | write operation |

|---------|---|-----------------|

| MAD04 = | 1 | read operation. |

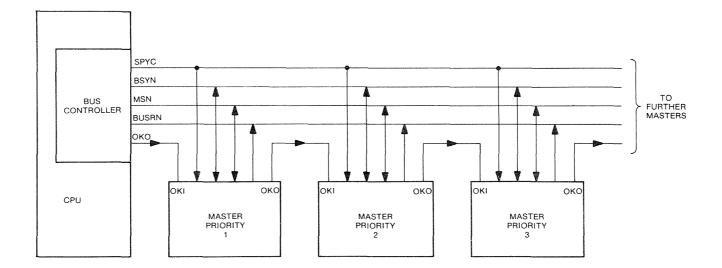

BIEC 0 to BIEC 5 Six signal lines which represent in encoded form the interrupt raised (other than internal interrupts) having the highest priority. The format is as follows: most significant least significant SCEIN A signal Scan External Interrupts sent by the CPU to control units at the end of each instruction which places on the BIEC 0 to 5 lines the 6 bits representing the highest priority external interrupt detected. A signal function accepted which is sent by a ACN control unit to the CPU to indicate that the requested function is accepted by the control unit. A signal bus request which is sent to the bus **BUSRN** controller in the CPU by a master which requires control of the bus to effect an exchange. **BSYN** A signal bus busy which is shared by all masters. It is set to "0" by the master which has been given control of the bus so that the exchange can commence without interruption. A signal master selected which is transmitted to all MSN Internal other masters by the master which has become use only master of the bus to block all activity of the priority selection chain. The signal is released when the master is ready for the next priority transaction. A signal scan priority chain sent by the bus SPYC controller to all masters in response to a BUSRN signal. The signal enables the highest priority master which has transmitted BUSRN to block the priority chain at its level.

| OKO<br>(internal use only)   | A signal generated by the bus controller after all masters have been alerted by SPYC It is sent to the master having the highest priority (determined by hard wiring in the priority selection chain).                                             |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OKI<br>(internal use only)   | A master which receives signal OKO regards the signal as OKI. It then retransmits a further OKO to the next master in the priority chain. The first master to receive OKI set to '1' and to retransmit OKO reset to '0' is next master of the bus. |  |

| CHA<br>(internal use only)   | A signal <i>character</i> transmitted to the memory by<br>the master which has control of the bus to indicate<br>whether the exchange is to be by character or by<br>word as follows:<br>CHA = 1 character operation<br>CHA = 0 word operation.    |  |

| WRITE<br>(internal use only) | A signal <i>write</i> transmitted to the memory by the<br>master which has control of the bus to write<br>information into memory or to read information<br>from memory as follows:<br>WRITE = 1 write into memory<br>WRITE = 0 read from memory.  |  |

| CLEARN                       | A signal <i>clear</i> transmitted by the CPU to all elements connected to the GP bus to cause a general reset to zero.                                                                                                                             |  |

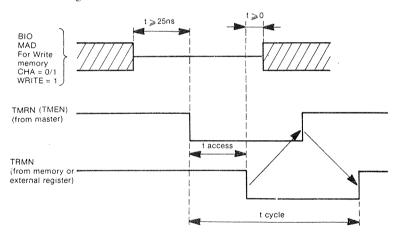

| TMRN<br>(internal use only)  | A signal <i>master to memory</i> transmitted by a master<br>to memory to validate the data on the BIO and<br>MAD lines during an exchange. The signal also<br>controls the timing of the exchange.                                                 |  |

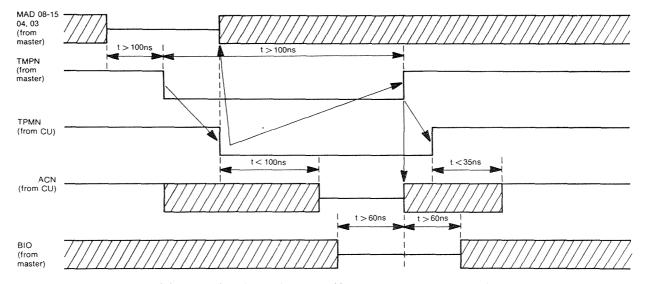

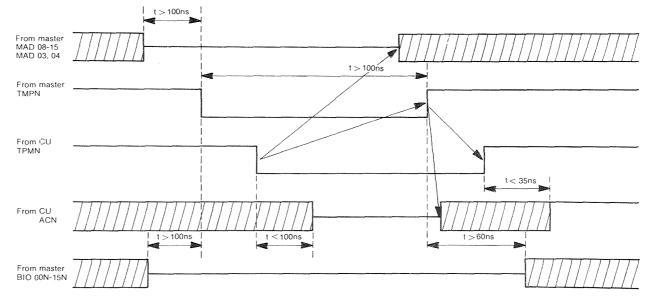

| TMPN                         | A signal <i>master to peripheral</i> transmitted by a master to a peripheral CU to validate the address of the peripheral CU and to initialize the exchange.                                                                                       |  |

| TMEN                         | A signal <i>master to external register</i> transmitted by<br>a master to a unit containing the addressed register<br>to validate the address and data of the register and<br>to control the timing of the exchange.                               |  |

| TRMN                         | A signal <i>register or memory to master</i> transmitted<br>by a unit controlling a register or by memory in<br>reply to TMEN or TMRN to indicate that the unit                                                                                    |  |

|               | transmitting the signal is in a condition to be read.<br>The signal is also used to terminate the exchange.                                                                                                                                                            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPMN          | A signal <i>peripheral to master</i> transmitted by the peripheral control unit concerned in reply to TMPN. It is also used to validate the response of the control unit and to terminate the exchange.                                                                |

| RSLN          | An Earth signal <i>reset line</i> transmitted by the CPU power supply (or external rack power supplies) and used to protect the peripherals during the switching on and switching off power sequence. The signal is also used to generate CLEARN when switching on.    |

| PWFN          | A signal <i>power fail</i> transmitted by the CPU power<br>supply (or external rack power supplies) to warn<br>the CPU that power failure has been detected. The<br>signal is also used as a facility to restart the system<br>at the point where it has been stopped. |

| 4 spare lines | There are 4 spare lines provided on the GP bus extension cable outside the CPU cabinet.                                                                                                                                                                                |

The programmed channel is the basic I/O transfer channel used to transfer data between the CPU and the peripherals or external registers one word or character at a time. The data are transferred, via the GP bus, under the control of a set of instructions and the channel operates at rates of up to 20,000 16-bit words per second. Details of all connections to the channel are given in Part 2 of this Section of the manual.

The channel can be used in Wait Mode, where each word or character is exchanged separately and the complete program is held up in a waiting loop between each exchange, or in Interrupt Mode where each word or character is still exchanged separately but the necessary instructions form part of an interrupt routine which allows the main program to continue whilst an exchanged is in progress. The wait mode (the slowest form of transfer) is rarely used.

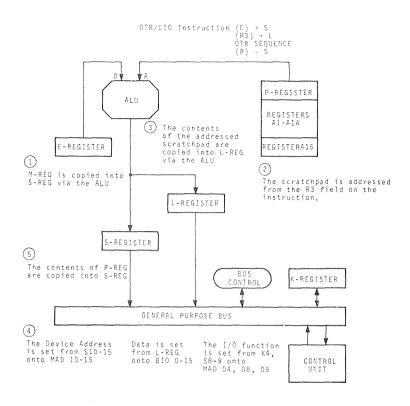

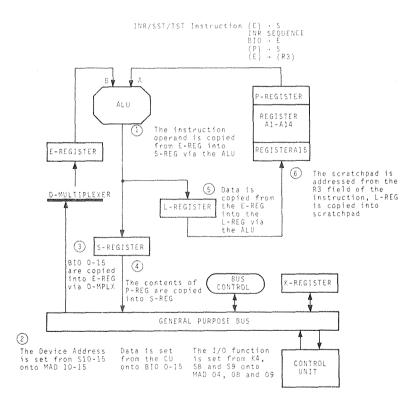

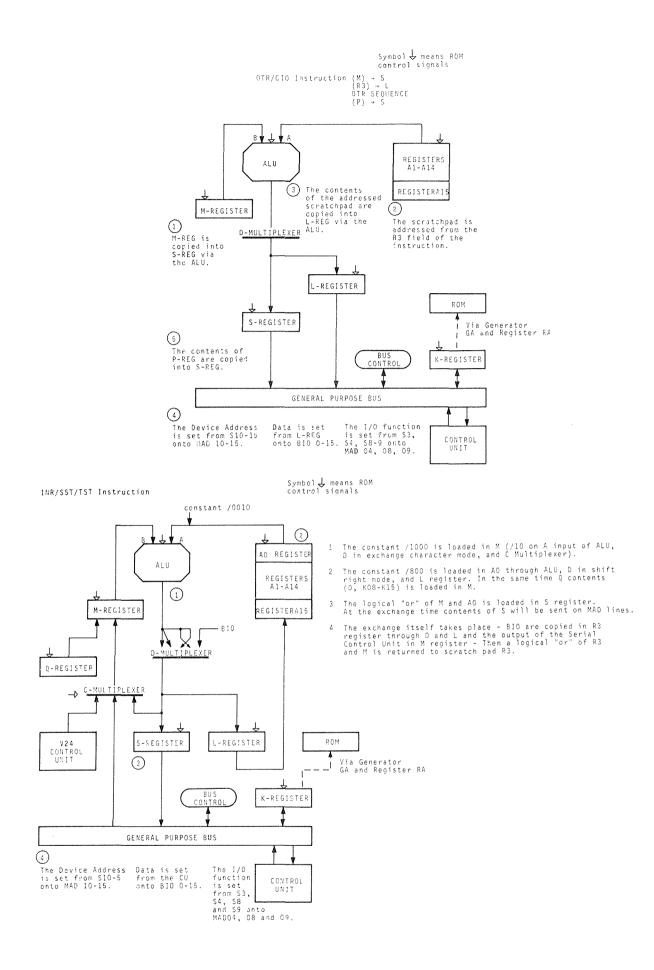

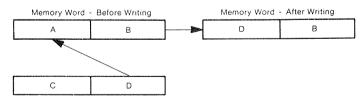

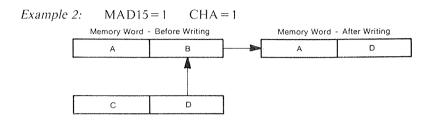

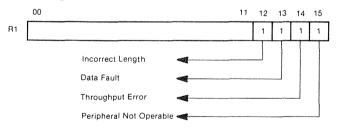

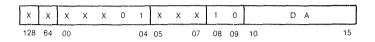

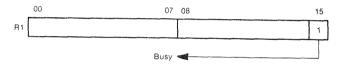

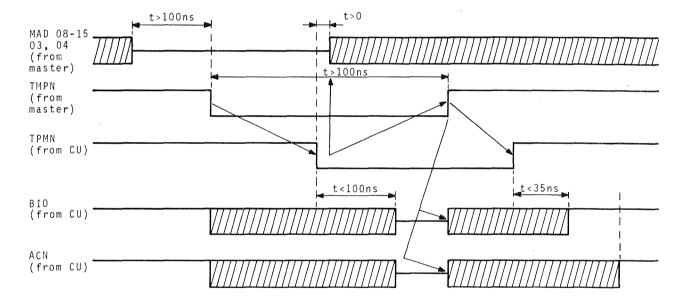

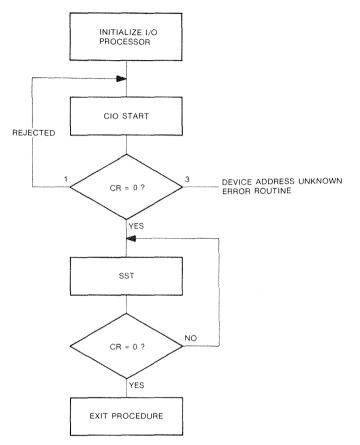

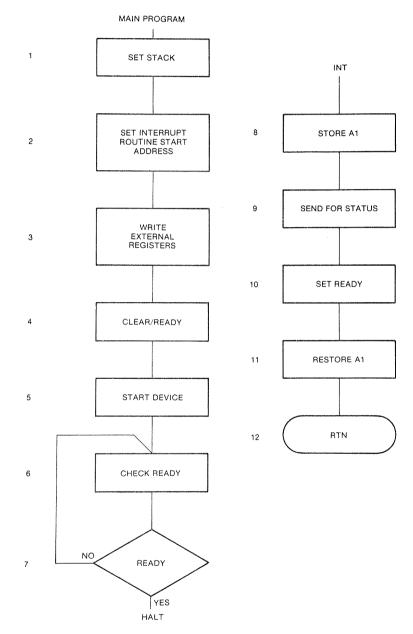

Figures 3.1 and 3.2 illustrate the Instructions flow for the P852M and the P856M/P857M computers respect-ively.